Copyright by **Jiajun Wang** 2019 The Dissertation Committee for **Jiajun Wang** certifies that this is the approved version of the following dissertation:

# Reuse Aware Data Placement Schemes For Multilevel Cache Hierarchies

Committee:

Lizy Kurian John, Supervisor Earl E. Swartzlander Jr Andreas Gerstlauer George Biros Mohit Tiwari

## Reuse Aware Data Placement Schemes For Multilevel Cache Hierarchies

by

Jiajun Wang

### DISSERTATION

Presented to the Faculty of the Graduate School of The University of Texas at Austin in Partial Fulfillment of the Requirements for the Degree of

### DOCTOR OF PHILOSOPHY

THE UNIVERSITY OF TEXAS AT AUSTIN May 2019 Dedicated to my family

### Acknowledgments

I would like to express my special appreciation and thanks to my advisor Prof. Lizy Kurian John for her tremendous guidance of my PhD study. I would like to thank her for the endless patience and encouragement to allow me grow up my research interest, for the immense knowledge to guide me in all the time of research, and for continuous support to help me in not only writing of this dissertation and all the other research papers. I could not have imagined having a better advisor and mentor for my PhD study, and my respect goes to her.

Besides my advisor, I would like to thank the rest of my dissertation committee: Prof. Earl E. Swartzlander, Prof. Andreas Gerstlauer, Prof. George Biros and Prof. Mohit Tiwari, for their insightful comments and constructive criticism to help me widen my research from diverse disciplines and improve this dissertation. I would also like to express sincere gratitude for the opportunity to collaborate with my internship mentors at ARM memory research team, Wendy Elsasser and Prakash Ramrakhyani. Thank you for your constructive comments and unfailing feedback in improving my research topic.

My PhD time will lose so much fun without the interaction with other graduate students. I would like to thank all the member of LCA research group: Dr. Jee Ho Ryoo, Dr. Michael Lebeane, Dr. Reena Panda, Shuang Song and Qinzhe Wu. Specifically, thanks Reena for helping me develop many research ideas as well as the countless coffee chats we had together. I am also grateful for the course projects and leisure activities with others: Dr. Zhuoran Zhao, Dr. Yazhou Zu, Dr. Wooseok Lee, Mochamad Asri and Kishore Punniyamurthy.

I would like to thank my mom and dad for making the start of my PhD journey possible. I can not be more grateful for their unwavering support of my decisions on the turning points in life. Thanks for sharing both joy and worries and always having faith in me.

Lastly, I will not reach the destination of this PhD journey without the support of my husband, Lu Zhang. Thanks for patiently proof reading every single word of my research paper and be the loyal and critical audience of my presentation. Thanks for always staying late with me till the last minute of paper submission, regardless of whether the deadline is at midnight or early morning. Thanks for giving me both encouraging words and agreeable melancholy during the most difficult time of my PhD. This doctorate is as much his as mine.

## Reuse Aware Data Placement Schemes For Multilevel Cache Hierarchies

Publication No. \_\_\_\_\_

Jiajun Wang, Ph.D. The University of Texas at Austin, 2019

Supervisor: Lizy Kurian John

Memory subsystem with larger capacity and deeper hierarchy has been designed to achieve the maximum performance of data intensive workloads. What grows with the depth and capacity is the amount of data movement happened between different levels of caches and the associated energy consumption. Prior art [65] shows that the energy cost of moving data from memory to register is two orders higher than the cost of register-to-register doubleprecision floating point operations. As the cache hierarchy grows deeper, the energy cost on the large amount of data movement between cache layers has become non-negligible. Energy dissipation of future systems will be dominated by the cost of data movement. Thus, reducing data movement through exploiting data locality becomes essential to build energy-efficient architectures.

A promising technique to improve the energy efficiency of modern memory subsystem is to adaptively guide data placement into appropriate caches with the performance benefit and energy cost of data movement in mind. An intelligent data placement scheme should only move data blocks with future re-reference into cache. As the working set size of emerging workloads exceeds cache capacity and the number of cores and IPs sharing caches keeps increasing, a data movement aware data placement scheme can maximize the performance of cache-sensitive workloads and minimize the cache energy consumption of cache-insensitive workloads.

Researchers have noticed that exclusive caches have better performance compared to inclusive caches. However, high performance improvement is always at odds with low energy consumption. The amount of data movement and energy consumption of exclusive caches is higher than inclusive ones. A few state-of-the-art CPU caching insertion/bypass policies have been proposed in literature. However these techniques are either at great expense of metadata overhead when adapting to exclusive caches, or they focus on reducing data movement at the sacrifice of performance. On the GPU side, designing efficient data placement schemes also faces great challenge. CPU caching schemes do not work for GPU memory subsystems, because the SRAM capacity per GPU thread is far smaller than the number per CPU threads. The capacity of GPU on-chip SRAMs is too small to hold large data structures in the GPU workloads. Data with frequent reuse is evicted before it is re-referenced which results in high GPU cache miss rate. Keeping the above shortcomings of prior work and key limitations in mind, this dissertation focuses on improving the performance and energy efficiency of modern cache subsystems of CPU and

GPU by proposing performance and energy sensitive data placement schemes.

This dissertation first presents a data placement for multilevel CPU caches to guide data placement into appropriate cache layers based on data reuse patterns. PC is utilized as the prediction heuristic based on the observation of good correlation between memory instruction and the locality of the data accessed by the instruction. Unlike prior art that includes great overhead for meta-data (e.g., PC) transmission and storage, a holistic approach to manage data placement is presented, which leverages bloom filters to record the memory instruction PC of data blocks. The proposed scheme incorporates quick detection and correction of stale/incorrect bypass decisions and an explicit mechanism for handling prefetches. This leads to energy efficiency improvement by cutting down wasteful cache block insertions and data movement.

To overcome the challenges on the GPU side, an explicitly managed data placement scheme in GPU memory hierarchy is presented in this dissertation. In order to improve data reuse of a popular HPC application and eliminate redundant memory accesses, data access sequence is rearranged by fusing multiple GPU kernel execution. Bank level fine-grained on-chip SRAM data placement and replacement is designed based on the microarchitecture of GPU memory hierarchy to maximize capacity utilization and interconnect bandwidth. The proposed scheme achieves the best performance and least energy consumption through reducing memory access latency and eliminating redundant data movement.

# Table of Contents

| Acknowledgments                                          | v    |

|----------------------------------------------------------|------|

| Abstract                                                 | vii  |

| List of Tables                                           | xiii |

| List of Figures                                          | xiv  |

| Chapter 1. Introduction                                  | 1    |

| 1.1. Problem Description                                 | 4    |

| 1.1.1. Challenges in CPU memory subsystems               | 4    |

| 1.1.2. Challenges in GPU memory subsystems               | 8    |

| 1.2. Limitations of Prior Research Work                  | 11   |

| 1.3. Overview of Proposed Research                       | 15   |

| 1.4. Thesis Statement                                    | 18   |

| 1.5. Dissertation Contribution                           | 18   |

| 1.6. Dissertation Organization                           | 20   |

| Chapter 2. Related Work                                  | 22   |

| 2.1. Schemes for Measuring Spatial and Temporal Locality | 22   |

| 2.2. Exclusive Caches and Data Replacement Policies      | 24   |

| 2.3. Data Placement Involving Software Level Management  | 28   |

| Chapter 3. Methodology                                   | 30   |

| 3.1. Simulation Infrastructure and Power Measurement     | 31   |

| 3.1.1. CPU performance and power measurement             | 31   |

| 3.1.2. GPU performance and power measurement             | 32   |

| 3.2. Workload Description                                | 33   |

| 3.2.1. CloudSuite                                        | 33   |

|        | 3.2.2. | SPEC CPU2006 benchmarks                                                     | 36 |

|--------|--------|-----------------------------------------------------------------------------|----|

|        | 3.2.3. | Kernel summation                                                            | 36 |

| Chapte | er 4.  | Data Locality Analysis and Micro-architectural In-                          | 38 |

| 4 1    | Б      | sights                                                                      |    |

| 4.1.   | -      | rimental Setup                                                              | 40 |

|        |        | Temporal locality profile                                                   | 41 |

| 4.2.   | -      | rsis of Temporal Locality                                                   | 42 |

|        |        | Micro-architectural insights                                                | 44 |

| 4.3.   | Analy  | rsis of Spatial Locality                                                    | 47 |

| 4.4.   | Sumn   | nary                                                                        | 50 |

| Chapte | er 5.  | Multicore CPU Data Placement Optimization                                   | 52 |

| 5.1.   | Prope  | osed Scheme                                                                 | 52 |

|        | 5.1.1. | Handling demand requests                                                    | 56 |

|        |        | 5.1.1.1. Applying bloom filter $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 57 |

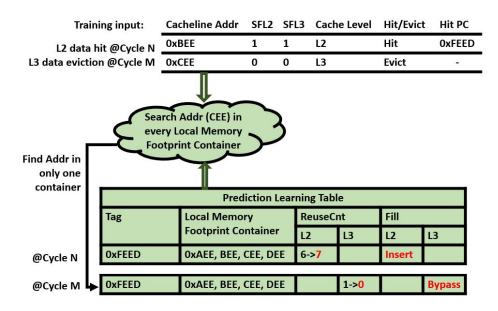

|        |        | 5.1.1.2. Prediction Learning table                                          | 58 |

|        |        | 5.1.1.3. Result table                                                       | 60 |

|        |        | 5.1.1.4. Learning from bypass decisions using empty blocks                  | 61 |

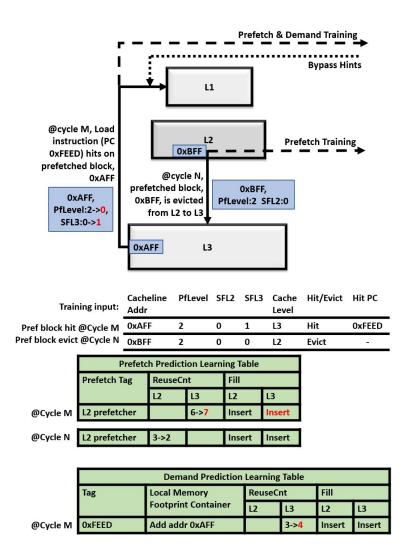

|        | 5.1.2. | Handling prefetch requests                                                  | 63 |

| 5.2.   | Evalu  | ation                                                                       | 65 |

|        | 5.2.1. | Evaluation results                                                          | 67 |

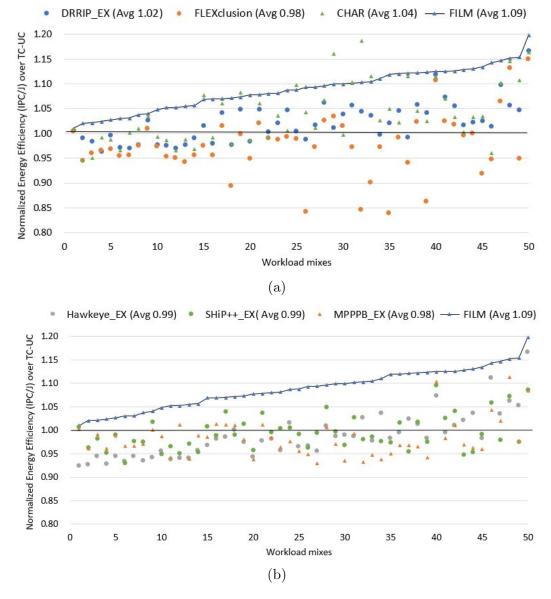

|        |        | 5.2.1.1. Energy efficiency                                                  | 68 |

|        |        | 5.2.1.2. Data movement                                                      | 73 |

|        |        | 5.2.1.3. Performance                                                        | 74 |

|        |        | 5.2.1.4. Comparison with RAP                                                | 78 |

|        | 5.2.2. | Hardware cost and design decisions                                          | 80 |

|        |        | 5.2.2.1. Hardware overhead comparison                                       | 80 |

|        |        | 5.2.2.2. Bloom filter analysis                                              | 81 |

|        |        | 5.2.2.3. Impact of "Utilize empty blocks" rule                              | 82 |

| 5.3.   | Summ   | nary                                                                        | 83 |

| Chapte       | er 6. GPU Data Placement Optimization   | 86  |  |

|--------------|-----------------------------------------|-----|--|

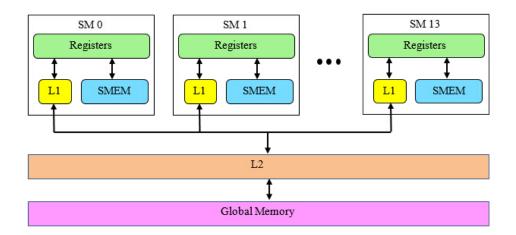

| 6.1.         | GPGPU background                        | 87  |  |

| 6.2.         | Kernel Summation application            | 89  |  |

| 6.3.         | Proposed Scheme                         | 91  |  |

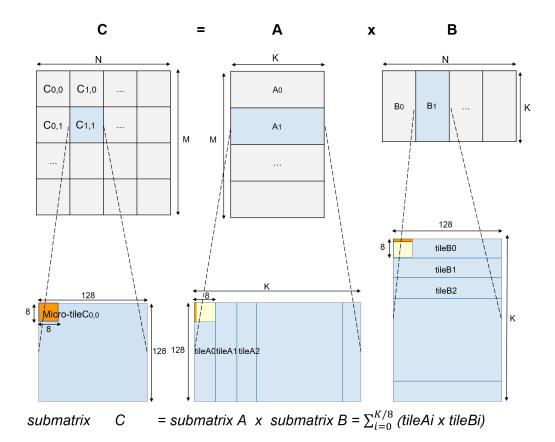

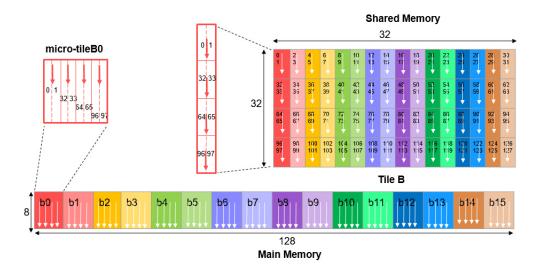

|              | 6.3.1. Data placement in GEMM           | 94  |  |

|              | 6.3.2. Shared memory data mapping       | 98  |  |

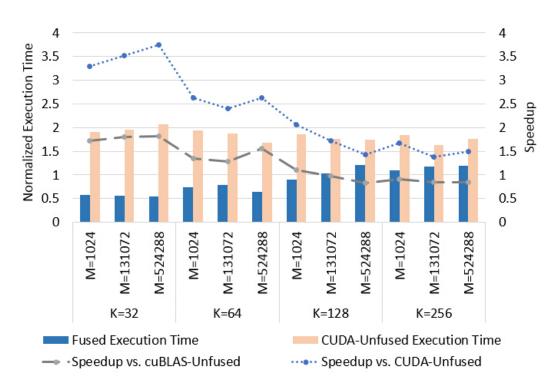

|              | 6.3.3. Kernel summation fused with GEMM | 101 |  |

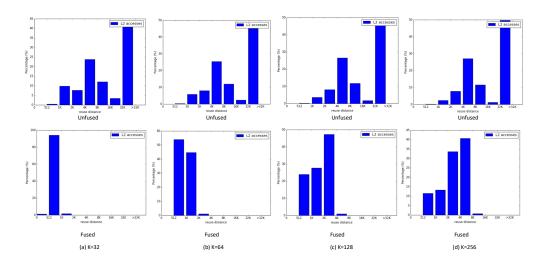

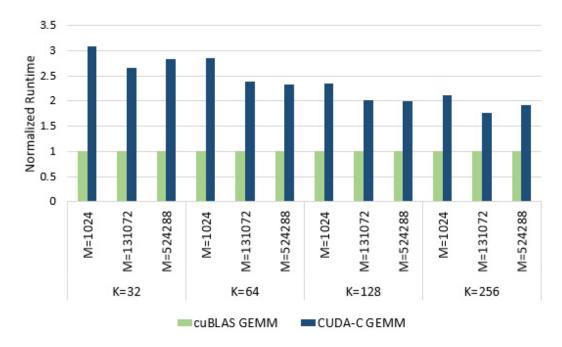

| 6.4.         | Evaluation                              | 105 |  |

|              | 6.4.1. Influence on data movement       | 110 |  |

|              | 6.4.2. Energy                           | 112 |  |

| 6.5.         | Summary                                 | 114 |  |

| Chapte       | er 7. Conclusion and Future Work        | 116 |  |

| 7.1.         | Summary                                 | 117 |  |

| 7.2.         | Future Work                             | 119 |  |

| Bibliography |                                         |     |  |

| Vita         |                                         | 148 |  |

# List of Tables

| 4.1. | System Configuration                                                                           | 40  |

|------|------------------------------------------------------------------------------------------------|-----|

| 4.2. | Workload characteristics                                                                       | 40  |

| 5.1. | Simulation parameters                                                                          | 66  |

| 5.2. | Workload mixes in Figure 5.5                                                                   | 70  |

| 5.3. | Workload mixes in Figure 5.7                                                                   | 76  |

| 5.4. | Comparison between FILM and RAP enhanced with FILM-like training on prefetch relative to TC-UC | 79  |

| 5.5. | FILM hardware budget (per core)                                                                | 80  |

| 5.6. | Overhead Comparison (per core)                                                                 | 80  |

| 6.1. | Configuration                                                                                  | 104 |

| 6.2. | FLOP Efficiency                                                                                | 108 |

| 6.3. | Energy Savings of <i>Fused</i> compared to <i>cuBLAS-Unfused</i>                               | 113 |

# List of Figures

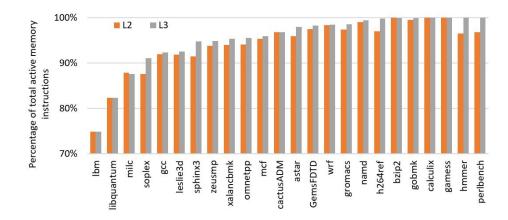

| 1.1. | Percentage of L1 evicted cache blocks getting reused at L2 and L3 in SPEC CPU2006 (average)                                                                               | 6  |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2. | L2 MPKI of kernel summation problem, with N=1024 in all cases                                                                                                             | 9  |

| 1.3. | Performance of inclusive cache orientated and PC-correlated al-<br>gorithms deteriorate if LLC is exclusive.                                                              | 11 |

| 1.4. | Normalized performance and LLC traffic of state of the art caching schemes over TC-UC.                                                                                    | 13 |

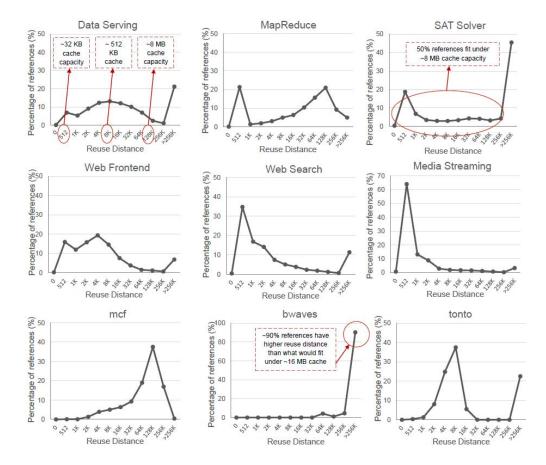

| 4.1. | Temporal locality analysis: The figure shows the approximate reuse distance panel. Y-axis presents percentage of memory references and x-axis presents the reuse distance | 41 |

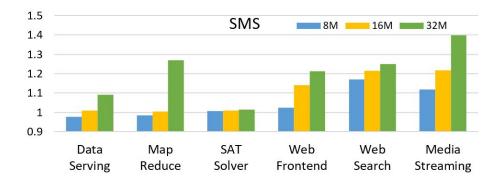

| 4.2. | Prefetching Sensitivity of LLC Size                                                                                                                                       | 44 |

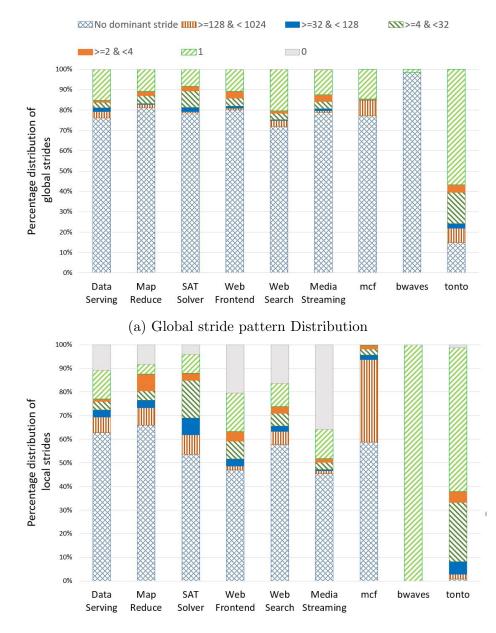

| 4.3. | Spatial locality analysis: Global/Local stride patterns in LLC access streams                                                                                             | 48 |

| 5.1. | Percentage of memory instructions with stable data locality .                                                                                                             | 54 |

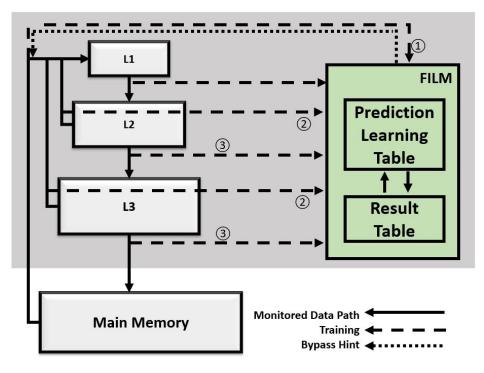

| 5.2. | Overview of the proposed FILM system                                                                                                                                      | 55 |

| 5.3. | Training of FILM on demand-fetched blocks. One Prediction<br>Learning table entry update at two different cycles                                                          | 59 |

| 5.4. | Training on prefetched blocks. Showing two different scenarios at two different cycle.                                                                                    | 64 |

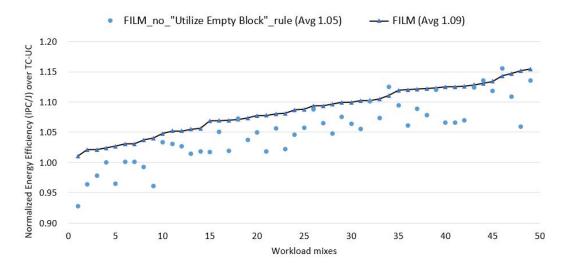

| 5.5. | Energy efficiency (IPC/J) of FILM and other schemes. Results normalized to TC-UC. The higher the better.                                                                  | 69 |

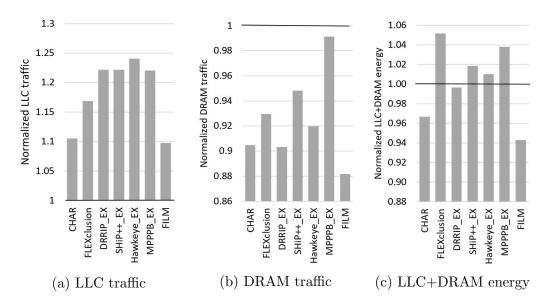

| 5.6. | The traffic and energy of shared memory resource (LLC and DRAM) of FILM and other schemes. Results normalized to TC-UC. The lower the better.                             | 73 |

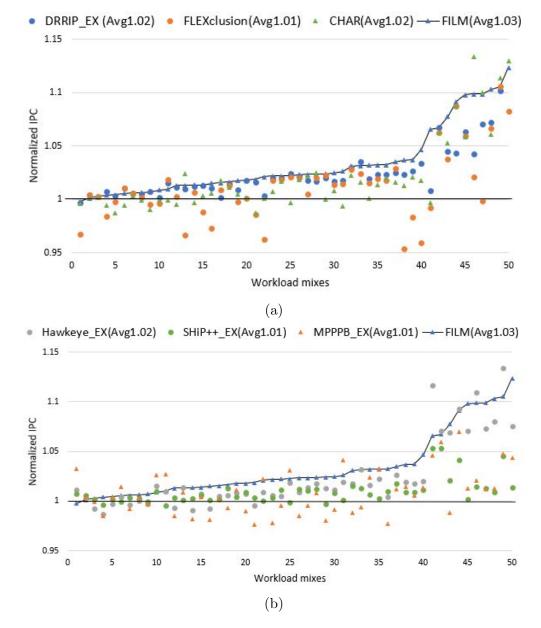

| 5.7. | IPC of FILM and other schemes. Results normalized to TC-UC. The higher the better.                                                                                        | 75 |

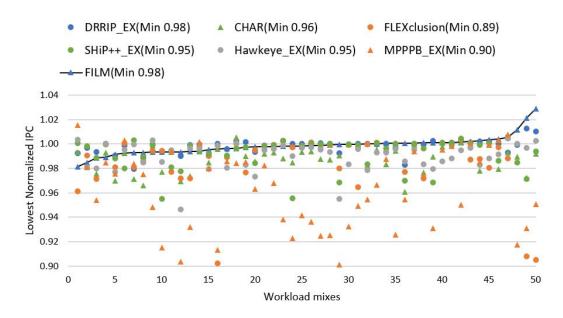

| 5.8. | Lowest normalized IPC of any co-running program. IPC reduc-<br>tion due to negative interference is least for FILM                                                        | 78 |

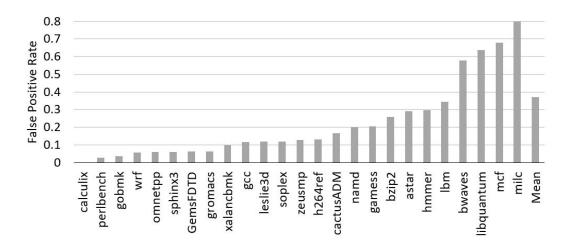

| 5.9. | Rate of multiple entry matches reported by FILM's bloom filter.                                                                                                           | 81 |

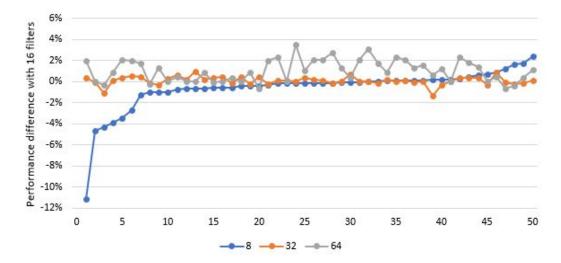

| 5.10. | Performance sensitivity to the number of bloom filters. IPC normalized to 16 bloom filters                                 | 83  |

|-------|----------------------------------------------------------------------------------------------------------------------------|-----|

| 5.11. | Energy efficiency of FILM and FILM without "utilize empty block rule". Results normalized to TC-UC. The higher the better. | 84  |

| 6.1.  | GPGPU memory hierarchy                                                                                                     | 87  |

| 6.2.  | GEMM algorithmic view                                                                                                      | 95  |

| 6.3.  | Data-thread mapping when loading $tileB$ into shared memory                                                                | 98  |

| 6.4.  | Execution time and speedup of the fused kernel summation in comparison with unfused implementations.                       | 106 |

| 6.5.  | Reuse distance profile of CUDA-Unfused and Fused approach at shared L2. $M=N=131072$                                       | 107 |

| 6.6.  | Execution time comparison of different GEMM implementations                                                                | 109 |

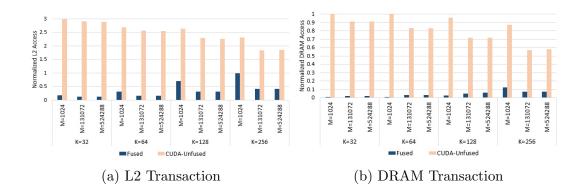

| 6.7.  | L2, DRAM transaction number normalized to <i>cuBLAS-Unfused</i> .                                                          | 111 |

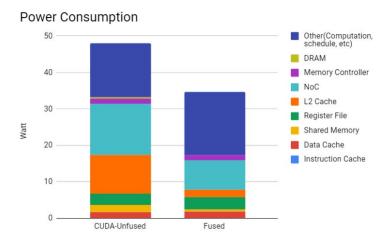

| 6.8.  | Power comparison between CUDA-Unfused and Fused approach. $M=N=1024, K=256$                                                | 111 |

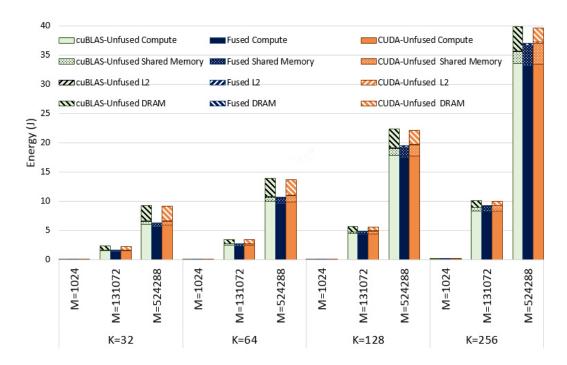

| 6.9.  | Energy consumption breakdown into Compute, Shared memory, L2, and DRAM                                                     | 112 |

## Chapter 1

### Introduction

In the era beyond the end of Denard's scaling, scaling throughput has become the driven force to scale microprocessor performance due to the inability to scale frequency. Performance improves by processing more threads concurrently using increased core counts and by employing micro-architectural techniques like SMT/SIMD. The number of threads in modern microprocessor SoCs is increasing as exemplified in 48 thread Arm based solutions [18] and 36 thread recently announced Intel solutions [43]. However, improving throughput by putting more cores together is not sustainable due to power and thermal management challenges. High energy bills of large data centers and limited battery life of edge devices have prompted efforts to make modern computer systems more energy and power efficient.

From the field of exascale supercomputer systems to the market of mobile edge devices, it has been commonly highlighted that energy dissipation of future systems will be dominated by the cost of data movement. Prior art [65] shows that the energy cost of moving data from memory to register is two orders higher than the energy cost of register-to-register double-precision floating point operations. In the server computing environment, around 28% to 40% of total processor energy consumption of scientific applications is spent on data movement [66]. Stories are similar to the domain of mobile application processors. The power consumption of solely working on fetching data from memory is on par with the mobile processors busy executing arithmetic operations under 100% utilization [107]. Prior art shows that as semiconductor process technology scales from 45nm towards 7nm and beyond, the compute energy scales down by 6X, whereas the energy associated with moving data across chip through interconnect does not scale as much [89]. The ratio between the energy cost of data movement and computation is expected to quickly grow in the future [71, 78].

Cache systems have been designed to achieve maximum performance for the workload. Still, the total cache capacity is often under-provisioned for data intensive workloads and under-utilized for cache-insensitive workloads. On energy efficient systems, maximizing performance at the cost of designing large caches is still desired for cache-sensitive workloads. Meanwhile, the energy consumption of large caches should not be wasted when running cacheinsensitive workloads. As the working set size of emerging workloads keeps growing, modern processors employ multiple levels of caches to address the "Memory Wall" between high speed processors and orders of magnitude slower main memory. In order to bridge this gap, the computer architecture field has witnessed the growing depth of cache hierarchy from adding a second level cache as the back up of L1 cache, to the three-level cache model widely used in modern commercial CPU chips, to inserting an L0 level between the processor and L1 as in line buffers [40] or filter caches [70], to another more level of system cache serving different IPs on the same SoC package, to innovative ideas of DRAM caches [115] (e.g., die-stacked DRAM). What grows with the depth and capacity of cache hierarchy is the amount of data movement that happens between different levels of caches and the associated energy consumption. It is common that caches account for more than 50% of on-chip die area and consume a significant fraction of static and dynamic power.

Scratchpads are fast on-chip RAMs mapped into the processors address space at a predefined address range. Scratchpad RAM is explicitly managed at software level, either by programmer or compiler. Compared to cache RAM, scratchpad RAM requires smaller chip area thanks to its simplicity in the control logic and hence it consumes less energy [14]. Software using scratchpad RAM has higher memory performance predictability compared to cache RAM which is highly dynamic. Because of this feature, scratchpad is popular on safety-critical embedded systems which have to meet certain real-time constraints [144]. Scratchpads are widely used in hardware accelerators as well. GPU chips from both NVIDIA and AMD provide programmers with scratchpad memory, which is called as "shared memory" in NVIDIA's term and "local data store" in AMD's term. Scratchpad memory enables efficient GPU thread communication within the same thread block, whereas thread communication through hardware managed caches usually causes frequent misses. Scratchpad is also used in other domain specific architectures to communicate intermediate results, e.g., input and output of hidden layers in neural network [63]. In order to achieve high performance from using scratchpads, it requires programmers to restructure their code and reorder data access sequences with hardware characteristics in mind.

### **1.1** Problem Description

#### 1.1.1 Challenges in CPU memory subsystems

Recent years have witnessed the rise of code and data footprints from emerging applications, whereas the CPU cache capacity per thread/core has reached limits due to the power and die area constraints. From the first generation of Intel Core i7 chip to the most recent Intel Core i9 design, the LLC capacity has been held to a maximum of 2MB per core during the past ten generations. Due to the diminishing return of performance on allocating larger caches [117], the performance benefit is negated by the increasing dynamic and static cache power. To improve the performance of data intensive workloads, prior research has looked at redistributing the available SRAM capacity across the various levels in the cache hierarchy and shown that many emerging workloads benefit from a larger L2 size [51, 72, 19]. Several recently announced microprocessor products appear to have conformed to this recommendation [148, 147]. Opting for larger L2 sizes however, implies that there would be greater overhead to maintain the inclusive property. In prior work, relaxing the inclusion requirement of LLCs has been shown to be beneficial with 3-12% improvements reported [51, 39]. This observation motivates exclusive caches in modern CPU cache hierarchy.

Performance and power consumption are always at odds while optimizing cache hierarchies. While exclusive caches will be high-performance as suggested above, due to the inherent difference of data block placement between an exclusive hierarchy and an inclusive hierarchy, the amount of data movement in exclusive hierarchy is generally larger than that of inclusive hierarchy [126]. Please note that in this dissertation, the terminology "inclusive hierarchy" is used to describe both strictly inclusive hierarchy and the nonstrictly inclusive hierarchy (which is also called as non-inclusive hierarchy in prior arts). The data movement within the non-strictly inclusive hierarchy is the same as the strictly inclusive hierarchy, except that when a data eviction happens in the lower level of cache, the same clean copy (if exists) in the upper level cache is not invalidated in the non-strictly inclusive hierarchy, whereas a back-invalidation is demanded in the strictly inclusive hierarchy. Different from inclusive hierarchies, only the top level cache of the multi-level exclusive caches is filled with LLC miss data, and the remaining levels serve as victim caches [64], which get filled upon evictions from the upper cache level regardless of cacheline dirty status. When a cache block is evicted from its current cache level, it is written back into the next lower level cache, evicting another block if necessary. If a cacheline in a non-top level cache receives a hit, the cacheline is invalidated from current level before fetched into the top level to maintain uniqueness as well as to make room for cachelines evicted from its upper level cache. A ping-pong trip between L1 and L3 includes all three levels of caches, as an L1 evict is typically inserted into L2 first and then into

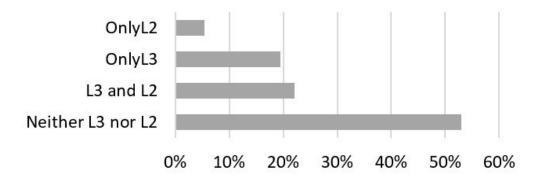

Figure 1.1: Percentage of L1 evicted cache blocks getting reused at L2 and L3 in SPEC CPU2006 (average)

L3. Large amount of on-chip bandwidth is consumed as data moves around the different levels of the cache hierarchy. There are two major causes of data movement in exclusive cache hierarchies, one is data moving from lower levels of cache to L1 due to cache hit, and the other is data moving from current level to its next level due to the eviction caused by cache replacement. Constraining data movement to L1 usually results in performance degradation because it sacrifices good L1 cacheline spatial locality and the high L1 hit rate, whereas reducing the data movement caused by eviction can be a good target for energy saving.

In order to quantify the (in)efficiency of data movement, data reuse of a dynamic cache block experiences at L2 and L3 is recorded. A dynamic data block is assumed to be a 64B (or other block size) block residing in the cache hierarchies. Dynamic cache blocks are categorized into four groups based on whether its reuse after gets evicted out of L1. The four groups are "onlyL2", "onlyL3", "L2 and L3", "neither L2 nor L3". Figure 1.1 illustrates the distribution of reuse across all dynamic cache blocks for SPEC CPU2006 suite. From the figure it is seen that among all the dynamic cache blocks evicted out of L1, only 20% get reused in both L2 and L3. Another 5% of data blocks only get reused in L2 but no further reuse after evicted out of L2. Approximately 20% of data blocks never get reused by the time they are evicted out of L2, but are reused in L3. More than 50% of dynamic cache blocks are never reused after they are evicted out of L1. This suggests that 80% of the workload working set has optimal cache location whereas insertion into other cache levels will not bring any additional benefit. Specifically, cache blocks in the "onlyL3" category should bypass L2 when evicted out of L1 and should directly insert into L3, and cache blocks in the "Neither L3 or L2" category should write back to main memory once they are evicted from L1.

Apart from reducing non-beneficial data movement between various levels of caches, another major source of improving memory subsystem energy efficiency is to reduce main memory (DRAM) accesses. The access latency of off-chip DRAM accesses is often 5-7X of LLC access latency [43] and DRAM energy has been reported to account for more than 25% of the energy in data centers [92]. While the LLC latency can be hidden with instruction level parallelism (ILP) and out of order execution, accesses to off-chip memory incur stalls in the compute pipeline. To improve memory performance and save repeated data movement between DRAM and compute logic, various cache insertion/replacement policies have been proposed to improve cache hit rate.

#### 1.1.2 Challenges in GPU memory subsystems

GPU has traditionally been an accelerator for graphics processing. In the past decades, due to the large amount of parallelism in the highperformance computing applications, GPU has been adopted as a general highperformance computing device (which is called as General Purpose GPU). The SRAM resource contention in GPU is extremely severe. The amount of SRAM capacity per GPU thread is less than 1KB, which is far smaller than the capacity of around 2MB SRAM per CPU thread. This is because GPU has much more threads than CPU but also much less on-chip SRAM capacity. There could be at maximum tens of thousands threads sharing GPU memory subsystem (e.g., 26624 threads in Maxwell architecture [7]), whereas the number of threads sharing the memory subsystem is limited by the number of CPU cores which can not be large. It is common that the LLC capacity per CPU core is around 2MB, and the total LLC capacity scales with the number of cores. On contrary, the capacity of GPU LLC (which is usually L2) is around 2MB large which is shared by all the GPU cores (i.e., "Streaming Multiprocessor" in NVIDIA terminology) and all the GPU threads. The design ideology behind the difference of CPU and GPU SRAM capacity per thread is that GPU, which is designed as a throughput-oriented machine, uses massive parallelism to hide latency; whereas the latency-oriented CPU uses large caches to hide latency. However, the current cache subsystem for GPU is inefficient for general purpose GPU computing. The first reason is because it results in high L2 miss rate. Although the performance loss is made up by parallelism,

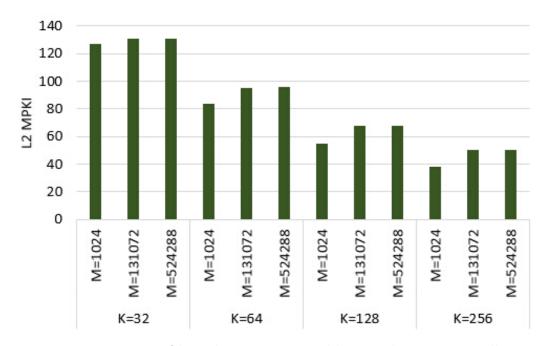

Figure 1.2: L2 MPKI of kernel summation problem, with N=1024 in all cases

the energy consumption is still huge. The second reason is because the GPU caches are too small to hold large data structures in the GPGPU workloads and the data with frequent reuse can be evicted before re-referenced due to the high contention between threads. Therefore, the data placement in the GPU cache hierarchy should be carefully handled.

Many widely used high performance computational kernels involve matrixmatrix multiplication (GEMM) and matrix-vector multiplication (GEMV) computational primitives [69]. These kernels can be decomposed into a serious of GEMM and GEMV calls with data dependencies between two calls. Basic Linear Algebra Subprograms (BLAS) provide a user-friendly interface to compute GEMM and GEMV. Different vendors provide their own highly optimized BLAS libraries for users, including the Intel's MKL [47] and the NVIDIA's cuBLAS [102] library. These BLAS libraries are often hand-optimized with assembly code and achieve over 80% of the peak performance. Although these are good options, they still have limitations. It is observed that using black-box BLAS libraries results in performance degradation when the geometric dimension of data set size is small. The first reason is because the performance of BLAS library becomes memory bound with small data size [95]. The second reason is that state-of-the-art GPU solutions which apply cuBLAS library cannot exploit much of the data locality. Using vendor-provided libraries brings performance benefit through the highly optimized BLAS, but it also sacrifices data locality because the intermediate matrix, as the return value of GEMM call, is written back to main memory due to its huge size not fitting into caches. Figure 1.2 illustrates the number of L2 misses per kilo instructions (MPKI) when applying the cuBLAS library in a kernel summation problem. There is high L2 MPKI number in dimension K = 32. Since L2 is the last level cache of GPU memory hierarchy, memory performance suffers a lot from high DRAM access latency and energy is wasted on redundant DRAM accesses. The kernel summation problem typically involves large data sets, and the long memory access latency is the crucial bottleneck of program execution. Redundant and slow intermediate value accesses to main memory suggests opportunities in performance and energy optimization.

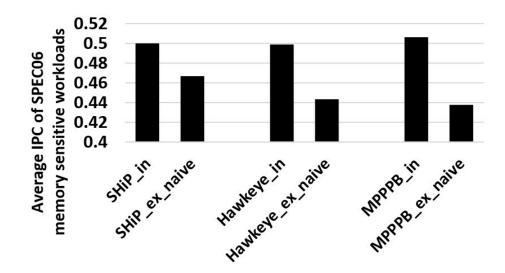

Figure 1.3: Performance of inclusive cache orientated and PC-correlated algorithms deteriorate if LLC is exclusive.

### **1.2** Limitations of Prior Research Work

The majority of state-of-the-art CPU caching insertion/bypass/replacement policies [52, 150, 50, 58, 33] are tuned for inclusive caches. PC-correlated algorithms are popular and yield high-performance in the field of inclusive cache design. However, a direct adaptation of PC-correlated cache bypass/replacement algorithm is ineffective. Figure 1.3 illustrates the performance comparison of three recently proposed PC-correlated schemes SHiP, Hawkeye and MPPPB [52, 150, 50, 58] between their original proposal tailored for inclusive LLC and the same design put under exclusive LLCs. The figure shows performance degradation when LLC is changed from inclusive to exclusive, which is largely due to the following two reasons. Firstly, the predictors that assume inclusive properties capture the reuse behavior of cacheline at certain cache level by observing subsequent hits in the same level. It is non trivial to apply such techniques to an exclusive hierarchy because upon observing a hit, cachelines in exclusives caches are evicted from the lower level and promoted to the upper level. Secondly, when making an insertion/bypass/replacement decision these schemes index into their predictors using the PC of the instruction that initiated the decision. For inclusive caches this PC corresponds to the instruction that causes the cachelines to be fetched from memory, but for exclusive caches, where lines are inserted into the lower level caches upon eviction, the only available PC is the one corresponds to the instruction that causes the eviction from the upper level. This does not have a good correlation with reuse behavior of the line that is being demoted, and so the efficacy of these schemes suffers. There are no PC-correlated algorithms tailored for exclusive caches because the required PC information is not available in exclusive caches. For exclusive caches, where lines are inserted into the lower level caches upon eviction, the PC information gets lost unless it is passed along with the cacheline across all the levels in the hierarchy. This can lead to inefficient use of space and also further exacerbate the problem of data movement.

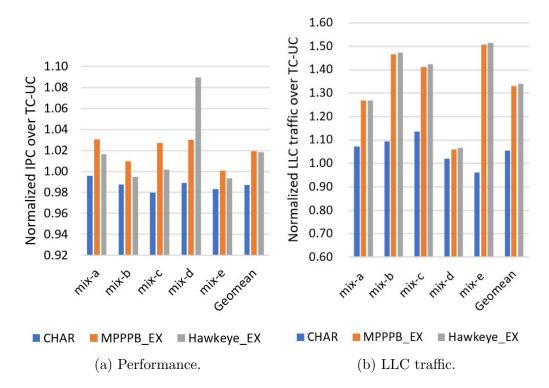

To make the performance matches with what was claimed in prior art, exclusive cache adaptations of the PC-correlated algorithms tailored for inclusive caches are devised by allowing unlimited hardware overhead to store training data (e.g., PC). The performance and data movement of three bypass and insertion algorithms for exclusive last level caches, CHAR [19], MPPPB\_EX [58] and Hawkeye\_EX [50], are compared using workload mixes from SPEC CPU2006

Figure 1.4: Normalized performance and LLC traffic of state of the art caching schemes over TC-UC.

suite. The comparison result is shown in the Figure 1.4, with IPC and LLC traffic normalized over TC-UC [39]. MPPPB\_EX and Hawkeye\_EX show better performance compared to CHAR, whereas CHAR generates less LLC traffic than MPPPB\_EX and Hawkeye\_EX. Specifically, Hawkeye\_EX demonstrates a 9% performance improvement compared to CHAR in mix-d by exploiting the data locality of lbm workload, whereas CHAR shows as large as 50% less LLC traffic than Hawkeye\_EX and MPPPB\_EX in mix-e due to reduced data movement from L2 to LLC (i.e., L2 eviction installed in LLC) of bwaves workload. The high-performance of MPPPB\_EX and Hawkeye\_EX are certainly

desirable, but the low data traffic of CHAR is also advantageous.

Several designs on GPU selective data placement have been proposed [153, 55, 156. GPU L1 cache is good candidate for bypassing because of the low L1 cache hit rate, low per-thread cache capacity and severe cache contention. Prior art uses the PC of memory instructions as indexes to predict dead blocks in L1, because the number of distinct memory instructions in a GPGPU workload is much smaller than the data size and the SIMD style instruction execution pattern makes it easy to learn data access pattern by sampling few thread groups. While these proposals save energy by preventing streaming data structure from burning cache power and hence improve performance by reducing cache pollution, they have performance limitations in the area of high performance computing applications, especially dense linear algebra problems. The first limitation is that prior art fails to exploit the temporal locality of large frequent accessed data structures. Scientific computing applications gain performance and energy efficiency by applying fast linear algebra libraries such as GEMM routine. As the majority of scientific computing applications are designed to use GEMM as much as possible, they can be decomposed into three major phase with data input output dependencies, which are pre-GEMM data preparation, GEMM computation, and post-GEMM data processing. Due to the data intensive nature of the scientific computing applications, the size of the intermediate data passing between the application phases is usually too large to be stored on chip. While bypassing schemes could save energy by directly moving data between computation units and the main memory without

storing data into caches, performance is not improved as bypassing algorithms do not help intermediate result to be reused in cache. The second limitation is that there is little performance improvement potential left for cache bypassing scheme on the GEMM computation, which is usually the most time consuming part and is calculated by calling BLAS libraries (e.g., cuBLAS library on NVIDIA GPU). BLAS library has been heavily hand optimized with assembly language by applying hierarchical blocking on all memory levels, even including register blocking. With temporal locality being maximized in GEMM, it becomes performance insensitive to the hardware cache bypassing scheme.

### 1.3 Overview of Proposed Research

Facing the challenge of reducing data movement and increasing memory subsystem energy efficiency, this dissertation focuses on developing techniques that can address above challenges via intelligent data placement, which yields the performance of state-of-the-art caching schemes, but with much reduced data movement, data traffic and energy consumption.

Analyzing and understanding the inherent patterns in the memory access streams of emerging applications is essential to design efficient data placement algorithms that minimize the off-chip memory traffic and improve overall memory performance. Through analyzing the temporal and spatial locality behavior of modern scale-out workloads, it is learned that data access pattern of emerging workloads exhibit a wide range of data reuse distance. At the capacity limits, memory sub-system is under-provisioned for data intensive workloads and over-provisioned for streaming workloads. Placing data blocks via untangling data reuse patterns saves system energy by preventing streaming data structure from moving around to waste cache capacity and burn cache power, and improves workload performance by allocating saved cache capacity to keep large frequently used data structures in cache. With the presence of prefetching scheme, workloads with long reuse distance and whose working set just fitting in cache benefit from increasing cache capacity, because large caches have high tolerance of the waste capacity on useless prefetch requests and enlarges the lifetime of early-fetched prefetch requests stayed in cache.

Most of the prior state-of-the-art data placement schemes target on improving the cache performance of inclusive caches, and they use the PC of the memory instructions as heuristics. In recent years there is a trend of moving from inclusive caches to exclusive caches because of the high performance advantage of exclusive caches. Applying prior arts on exclusive caches, however, requires PC information stored in every single cache block over the entire cache hierarchy, which costs a significant amount of training data storage and additional data movement energy as the PC moves along with the data block through interconnect. Aimed at addressing the energy cost of data movement and to devise an effective predictor for an efficient and scalable multi-level CPU exclusive cache hierarchy, this dissertation proposes a FILtered Multilevel (FILM) caching policy, which achieves good performance with reduced levels of data movement. As data blocks move around different level of caches, FILM uses centralized structure to store the PC of the access that causes DRAM fetch, rather than holding the PC along with data blocks which requires additional overhead at every level of the cache hierarchy. Specifically, bloom filter is used to overcome the challenges associated with capturing PCbased information in exclusive caches in an efficient manner. When there is free space in the bypassed cache layer, FILM overrides the initial prediction and allows cache block insertion into the cache level achieving more low latency hits. FILM also incorporates an explicit mechanism for handling prefetches, which allows it to train differently for data from demand requests versus prefetch requests. By incorporating quick detection and correction of stale/incorrect bypass decisions, FILM significantly reduces cache block installations and data movement,

However, this approach is not sufficient to unveil the potential of reusing large intermediate data structure in GPU memory subsystem, because the GPU on-chip SRAM capacity is fairly small in the massive multithreading environment and the intermediate result between two software phases is often too large to fit into GPU on-chip SRAM. Redesigning application source code with data reuse and data placement across GPU cache hierarchy in mind is the solution to this problem. In this dissertation, kernel summation is selected as an example to illustrate the performance and energy benefit of managing data placement using scratchpad in GPU. GPU utilizes fast explicitly managed scratchpad memories, which is also called as shared memory in NVIDIA GPU, to enable inter-thread communications and hide long memory access latency. The proposed data placement scheme yields both high performance and low energy consumption by fusing all steps of kernel summation into the GEMM code structure and optimizing memory access ordering to make good use of shared memory and cache hierarchy. Specifically, the kernel summation problem is decomposed into individual tasks with few dependencies and strike a balance between finer grained parallelism and reduced data replication. Thread to data mapping is organized in an interleaved way to achieve full memory bandwidth utilization, and the orders of accessing matrix elements from scratchpad ram is managed to avoid shared memory load and store bank conflicts.

### 1.4 Thesis Statement

Intelligent data placement across memory hierarchy based on their locality can reduce the amount of data movement and insertions over the memory hierarchy. This saves memory subsystem energy, reduces cache misses, and significantly improves system energy efficiency.

### **1.5** Dissertation Contribution

This dissertation makes several contributions to improve the energy efficiency of computing systems via intelligent data placement across multiple cache layers by taking the performance and energy effect of data movement into account. The key contributions of this dissertation are summarized below.

• The first contribution of this dissertation is a detailed memory access

pattern analysis of emerging computer workloads. It is observed that data access patterns of emerging workloads exhibit a wide range of data reuse distances. It is difficult to optimize a memory hierarchy for multiple reuse distances, as different optimizations may be needed for large or small reuse distances. Large reuse distance patterns can interfere with optimizations done for small reuse patterns. This observation motivates filtering and untangling of data reuse patterns to reduce data movement and system energy. System energy is saved by preventing streaming data structures from moving around and wasting cache capacity and cache power. Workload performance is improved by allocating saved cache capacity to keep large frequently used data structures in cache.

• The second contribution of this dissertation is a FILtered Multilevel (FILM) caching policy for exclusive cache hierarchies. A locality filtering mechanism with bloom filters and predictors is presented to capture PC-based guidance in a multi-level exclusive cache hierarchy with minimal hardware overhead. The proposed solution learns about the correctness of bypass decisions and adaptively guides data placement into appropriate cache layers based on data reuse patterns. The solution also makes prefetch aware training/learning of bypass/placement decisions. The proposed scheme demonstrates significant energy efficiency improvements and reduction in on-chip data movement. FILM improves overall energy efficiency by 9%, compared to the second highest of 4% from CHAR. • The third contribution of this dissertation is a code fusion technique for improving GPU data locality. It involves fusing of a series of GPU kernels in order to reduce data movement. With an example of kernel summation problem, this dissertation presents a fused technique that maximizes data locality using scratchpad memory. Data access sequence and placement is manually optimized based on the microarchitecture of GPU memory hierarchy to maximize GPU memory subsystem utilization via eliminating redundant data movement and main memory accesses. In order to optimize data accesses sequence, threads are mapped to matrix elements in an interleaved way, and matrix elements are reordered to avoid any load and store bank conflicts. The proposed scheme provides up to 1.8X performance speedup and 33% of total energy saving.

### **1.6** Dissertation Organization

This dissertation is organized as follows. Chapter 2 provides background about prior data placement schemes. Chapter 3 presents the evaluation framework used in this dissertation and explains the set of benchmarks and high-performance computing kernels that were used. Chapter 4 presents a detailed analysis of memory access pattern on modern scale-out workloads. Chapter 5 presents details of PC-correlated locality filtering approaches for exclusive cache hierarchies by exploiting data temporal locality. Chapter 6 presents an explicitly managed data placement scheme in GPU memory hierarchy for reducing data reuse distance of high-performance computing kernels on the state-of-the-art GPU. Chapter 7 concludes this dissertation with a summary of the contributions of the dissertation and suggestions for future research opportunities.

# Chapter 2

# **Related Work**

This chapter briefly describes the metrics used to capture data locality and provides an overview of the state-of-the-art research underlying this dissertation.

# 2.1 Schemes for Measuring Spatial and Temporal Locality

Broadly, temporal locality and spatial locality are captured using reuse distance and stride patterns respectively in this dissertation. Good temporal locality indicates short time period between adjacency accesses to the same address (i.e., if a particular memory location is referenced, then it is highly possible that the location will be re-referenced in a near future). Good spatial locality indicates accessing neighboring memory locations within a short time period (i.e., if a particular memory location is referenced, then it is highly possible that its nearby locations will be re-referenced in a near future).

Data Reuse distance, also known as Mattson's stack distance [96] is a powerful metric to capture the temporal locality of programs. The reuse distance of a reference in a memory address trace is defined as the number of distinct memory references between two successive references to the same location. Essentially reuse distance captures the number of intervening references between reuse of an address. If references are put into a stack, it indicates the depth at which some reused data can be located in the stack. The percentage of data references that exhibit a specific reuse distance can be computed. The distribution of such a metric for a variety of reuse distances provides an excellent picture of the potential performance of the workload with various cache sizes. Capturing the stack distance distribution essentially captures the performance of multiple cache sizes in one simulation using a single very large fully associative cache-like model. By doing so, the stack distance approach not only provides performance of caches with different sizes but indicates the total memory footprint of each workload. For example, if the workload has a combined instruction and data footprint smaller than the stack depth, the amount of valid data in the cache (assuming the cache is invalid at simulation start) represents the total memory footprint of the workload.

Strides per memory instruction (local) and memory reference stream (global) are used to characterize the spatial locality of data accesses. Local stride is defined as the difference between consecutive effective memory addresses localized per memory instruction. Local stride a good estimation of the most frequently used stride values per memory instruction and the number of memory references that it was used for. Global stride is defined as the difference between consecutive memory addresses and is used to analyze the stride-based behavior when seen across the entire global stream of memory accesses. This approach of characterizing and portraying the stride access patterns in terms of 64-byte blocks is similar to the approach adopted by Joshi, et al. [60] for SPEC CPU2000 benchmarks. Both local and global strides are computed at the granularity of 64-byte cache blocks.

### 2.2 Exclusive Caches and Data Replacement Policies

There have been several studies on intelligent cacheline bypass/placement. A group of researchers have studied the energy and performance impact of cache bypass on the first level cache [25, 10, 32, 135, 53], while another group of researchers focus on the last level [9, 31, 68, 82, 152, 88]. All these techniques only target single level of cache without addressing the problem from the perspective of the entire cache hierarchy. Wu, et al. propose Signature based Hit Predictor (SHiP) [150], a sophisticated cache insertion mechanism. SHiP predicts whether the incoming cache line will receive a future hit by correlating the re-reference behavior of a cache line with a unique signature, such as memory region, program counter, or instruction sequence history based signatures. The SHiP implementation compared in this dissertation uses program counter as the signature. Jain, et al. propose Hawkeye [50], a cache replacement policy which learns from Belady's algorithm by applying it to past cache accesses to inform future cache replacement decisions. Hawkeye is consisted of an OPTgen algorithm which uses the notion of liveness intervals to reconstruct Belady's optimal solution for past long cache accesses, and a predictor which learns OPT's behavior of past PCs to inform eviction decisions for future

loads by the same PCs. Jimenez, et al. propose Multiperspective Placement, Promotion, and Bypass (MPPPB) [58], a technique that predicts the future reuse of cache blocks using seven different types of features to capture various program properties and memory behavior. MPPPB optimizes three aspects of cache management block placement, replacement, and bypass. The set of features used in MPPPB include data address, last miss, offset and program counter.Its predictor is organized as a hashed perceptron predictor indexed by a diverse set of features, and the final prediction result is an aggregation of many predictions taking into account each prediction's confidence.

LRU policies have been generally seen to be ineffective [15] for exclusive caches. Invalidating lower level cachelines on hit poses challenges on replacement policies which are designed with non-exclusive hierarchies in mind and make replacement structure update based on the number of cache hits. For example, RRIP [52] replacement policy learns re-reference behavior of a cacheline through attaching an RRPV per cacheline whose value implies whether the cacheline will be re-referenced in near future or distant future. Rereference Prediction Value (RRPV) indicates the distance of a block from its next access. An RRPV of zero implies that a cache block is predicted to be rereferenced in the near-immediate future. Hawkeye [50] adopts the idead of RRPV in its algorithm as well. However, these replacement policies can not be directly applied to exclusive caches, because the cacheline is invalidated on hit and the information of such re-reference is lost along with the invalidation. In the original RRIP proposal, RRPV is gradually decremented when a cacheline sees a hit; or gets steadily incremented during victim selection till one of RRPV in the same set reaches the maximum. As RRPV value is lost on a cacheline hit due to invalidation, an exclusive LLC is unable to preserve cache lines that have been re-referenced. Jaleel, et al. [51] presented modifications required for RRIP to be applied to exclusive LLC (DRRIP\_EX) by adding an SFL3 bit per cacheline and condensing the re-reference information into the SFL3 bit. Specifically, the SFL3 bit is set when a cacheline gets hit at L3. On LLC insertion, if the line was originally served from memory (SFL3 is zero), it is predicted as reuse in distant future; if the line was originally served from L3 (SFL3 is one), it is predicted as reuse in near future. This paper extends this idea to both exclusive L2 and exclusive LLC by adding an SFL2 bit. SFL2 and SFL3 are set when a cacheline sees a hit and serves the data request from L2/L3, and are reset when the cacheline is evicted from L2/L3 to make room for new blocks.

Gaur, et al. explore insertion and bypass algorithms for exclusive LLCs and propose a number of design choices for selective bypassing and insertion age assignment (TC-UC). LLC bypass and age assignment decisions are based on two properties of a block, trip count and use count.

Chaudhuri, et al. propose CHAR [19], cache hierarchy-aware replacement algorithms for inclusive LLCs and applies the same algorithms to implement efficient bypass techniques for exclusive LLCs in a three-level hierarchy. The CHAR algorithm learns the reuse pattern of the blocks residing in the L2 cache to generate selective replacement hints to the LLC. Sim, et al. propose FLEXclusion [126] which dynamically switches between exclusion and non-inclusion depending on workload behavior. FLEXclusion shows significant data traffic reduction compared with exclusive caches and moderate performance improvement with non-inclusive caches. While FLEXclusion dynamically changes between the exclusive and non-inclusive to get the benefit of high performance of exclusive caches and low data traffic of non-inclusive caches, FILM's goal is to improve exclusive caches performance and reduce data traffic by learning bypass hints.

Sembrant, et al. present a Reuse Aware Placement (RAP) policy [123] to optimize data movement across the entire cache hierarchy. RAP dynamically identifies data sets and measures their reuse at each level in the hierarchy. Each cache line is associated with a data set and consults that data set's policy upon eviction or installation. RAP selects a group of cachelines (called learning blocks) to help adapt changes in application and instruction behavior by ignoring bypass decisions upon installation. RAP changes placement decision from bypass to install when the number of reuse of these learning blocks reaches a threshold. RAP experiences performance degradation as an incorrect bypass decision may have caused additional cache misses before it is corrected. Another factor leading to RAP's low performance is the absence of making special training effort on the prefetch requests. Moreover, RAP involves huge hardware overhead as it requires every cache block in the cache hierarchy to maintain a 12-bit large instruction pointer field.

## 2.3 Data Placement Involving Software Level Management

In addition to hardware support data placement, there are special ISA support for cache bypassing in commercial processors. X86 ISA provides bypass instructions for reads/writes with no temporal locality [99]. For example, MOVNTI (Store Doubleword Using Non-Temporal Hint) instruction performs an operand store operation using a non-temporal hint to minimize cache pollution during the write to memory. When executing the MOVNTI instruction, the processor does not write the data into the cache hierarchy, nor does it fetch the corresponding cache line from memory into the cache hierarchy. Similarly, ARM ISA provides LDNP and STNP instructions (non-temporal load and store) that perform a read or write of a pair of register values. They also give a hint to the memory system that caching is not useful for this data. There are similar ISA supports such as the ld.cg instruction in the GPU architecture as well. Id.cg specifies that a load bypasses L1 cache and is cached only in L2 cache and below.

Software programmers can either encode data placement hints in the application code to directly inform hardware about future data access pattern, or precisely control when to fetch a new data block and where to place data using scratchpad memory. Scratchpads are fast on-chip RAMs mapped into the processors address space at a predefined address range. Scratchpad RAM is explicitly managed at software level, either by programmer or compiler. Compared to cache RAM, scratchpad RAM requires less chip area thanks to its simplicity in the control logic and hence consumes less energy [14]. Software using scratchpad RAM has higher memory performance predictability compared to cache RAM which is highly dynamic. Because of this feature, scratchpad is popular on safety-critical embedded systems which have to meet certain real-time constraints [144]. Scratchpads are widely used in hardware accelerators as well. GPU chips from both NVIDIA and AMD provide programmers with scratchpad memory, which is called shared memory in NVIDIA's term and local data store in AMD's term. Scratchpad memory in GPU enables threads within a thread block to communicate with each other efficiently, as communicating through hardware managed caches usually leads to frequent misses. Scratchpad is also used in other domain specific architectures to communicate intermediate results, e.g., between neural network layers [63]. While scratchpads provide powerful tool to help programmer achieve high memory performance, in order to make full use of scratchpads it often requires programmers to restructure their code and reorder data access sequences with hardware characteristics in mind.

# Chapter 3

# Methodology

To evaluate the effectiveness of proposed data moving management schemes proposed in this dissertation, a combination of techniques involving measurements on real hardware systems and simulations is used. The CPU and GPU simulators used in this dissertation include ChampSim, which is a trace-based cycle-accurate simulator derived from the 2nd Cache Replacement Championship (CRC2) simulator [28], and GPGPU-Sim [13], which is a widely popular research GPU simulator. Traces feed into the ChampSim simulator is taken using PIN [90], a program analysis tool with dynamic instrumentation. Measurements of cuda application performance is performed on real hardware systems and the performance data is get from performance counters with the nvprof [6] profiling tool provided by NVIDIA. Dynamic power and energy consumed by the various policies is estimated using McPAT [84] and GPUWattch [79]. In terms of workloads, this dissertation uses a wide variety workloads, ranging from big-data workloads like CloudSuite [103], to high-performance scientific kernels, to general-purpose benchmarks suites like SPEC CPU2006 [42]. The rest of this chapter presents an overview of each tool and also a description of the different workloads/benchmark suites used to evaluate the proposed schemes.

# 3.1 Simulation Infrastructure and Power Measurement3.1.1 CPU performance and power measurement

This dissertation uses ChampSim, a cycle-level architecture simulator. It models the detailed out-of-order pipeline stages and memory system including cache-hierarchy and memory controller. ChampSim uses Intel's Pin tool to generate instructions traces with instruction pointer, register reads/writes, memory addresses and other information such as branch. Pin is a dynamic binary instrumentation tool and performs instrumentation at run time on the compiled binary files. The instruction traces are feed into the back-end simulation engine. The cache hierarchy of ChampSim can be configured with various levels and different parameters (e.g., cache capacity, associativity, access latency), and each caches can be configured with its different prefetching schemes and replacement policies. The default cache inclusivity of ChampSim is non-inclusion, but can be modified to exclusion. Similarly, the number of tenants sharing one cache can also be modified. ChampSim can be configured for both single core and multicore environment, and it gathers detailed statistics counters including IPC, branch performance (e.g., misprediction rate), cache performance (e.g., insertions, hits and misses of each access type) and memory performance (e.g., row buffer hits and misses per DRAM channel).

Except for using ChampSim to evaluate the performance of proposed schemes, the performance statistics gathered from ChampSim are fed into Mc-PAT to generate power and area number. McPAT is an architectural integrated power, area and timing modeling framework with a design constraint of target clock rate. It specifically targets on the area and power modeling framework for manycore processor, with a wide configurable range of core types (e.g., in-order or out-of-order, homogeneous or heterogeneous), uncore (e.g., interconnect and LLC), system I/O and memory controller components. McPAT provides XML interfaces to set up parameters of target architecture designs, and performance statistics captured by a performance simulator.

### 3.1.2 GPU performance and power measurement

This dissertation uses nvprof [6], an easy-to-use command line interface to access the processor performance counters on real GPU machines, to measure the performance of proposed schemes. NVIDIA GPU's nvprof is a profiling tool which enables data collection of a timeline of CUDA-related activities on both CPU and GPU. This profiling tool collects kernel execution, memory transfers, memory set and CUDA API calls and events or metrics for CUDA kernels.

Directly measuring power via hardware sensors is generally considered the most accurate way to measure power consumption. However, this approach is not available as the GPU related work in this dissertation is performed on the cloud server and neither external nor internal hardware power sensors are available. Therefore, this dissertation uses GPUWattch to evaluate the energy efficiency of proposed scheme. GPUWattch is a configurable cycle-level GPU power model built on top of a well-developed GPU performance simulator, GPGPU-Sim. GPUWattch estimates the power of GPU micro-architectural components based upon the corresponding power model in McPAT simulators and incorporates new micro-architectural simulated components by extending McPAT.

### 3.2 Workload Description

### 3.2.1 CloudSuite

Cloud computing is gaining popularity due to its ability to provide infrastructure, platform and software services to clients on a global scale. Using cloud services, clients reduce the cost and complexity of buying and managing the underlying hardware and software layers. CloudSuite is a benchmark suite for cloud services. It includes six major benchmarks.

**Data Serving** - There has been a significant increase in the number and diversity of NoSQL database solutions since recent years. Compared with SQL, NoSQL database provides a more flexible storage model and stronger scalability to higher data set sizes/cluster sizes. Several NoSQL data storage solutions [1, 5, 8] are used as back-ups for large Web applications such as Google Earth and Facebook Inbox. In this workload, the 15GB Yahoo! Cloud Service Benchmark (YCSB) data set is used to evaluate the performance of the Cassandra 0.7.3 database. The server load is generated using YCSB 0.1.3 client [27], which sends requests with a 95: 5 read to write request ratio in Zipfian distribution.

MapReduce - MapReduce is the computational model that is able to handle large-scale analysis, cluster/filter large amounts of data processes, and spread computation among a group of machines. These machines first perform a map function in which data are filtered, and then conduct a reduce function in which results from different machines are aggregated. This workload benchmarks a node of a four-node Hadoop 0.20.2 cluster. A Bayesian classification algorithm, which attempts to guess the country tag of each article in a 4.5GB set of Wikipedia pages, runs on it. One map task is started on one core with 2GB Java heap assigned.

Media Streaming - Thanks to high-bandwidth internet connectivity, recent years have witnessed an explosion in the accessibility to media streaming services such as YouTube and NetFilx, etc. Such streaming services take advantage of large computing clusters to process and transmit media files in diverse formats in a high speed. In this workload, the Darwin Streaming Server 6.0.3 is used. It serves videos of varying duration (from 1 min (1.6GB) to 10 min (>10 GB)) by using the Faban driver [2] to simulate the clients. The benchmark setup uses a low bit-rate video stream to shift stress away from network I/O.

**SAT Solver** - Symbolic execution is heavily used in hardware and software verification. Due to the complexity of this algorithm, it becomes tractable when the computation is partitioned into smaller sub-problems and distributed to the cloud where a large number of SAT solver processes are hosted. Since modern data center consists of heterogeneous machines, a worker-queue model with centralized load balancing is usually applied to re-balance tasks across a dynamic pool of unequal computer resources. Large scale computation is

adapted to the worker-queue model meanwhile minimizing communication overhead. Klee SAT Solver is an important component of the Cloud9 parallel symbolic execution engine [24]. It is set up as one instance per core. Input traces are generated by Cloud9 by symbolically executing the command-line printf utility from the GNU CoreUtils 6.10 using up to four 5-byte and one 10-byte symbolic command-line arguments.

Web Frontend - Web services should be fault-tolerant, widely-available and be of dynamic scalability. Such requirements necessitate web services to be hosted in the cloud. There are typically three roles within the web service architectures: a load balancer to distribute independent client requests, a web server to serve client requests, and middleware to store the state in the back-end database. We characterize a front end machine serving Olio, a Web 2.0 web-based social event calendar. Nginx 1.0.10 - with a built-in PHP 5.3.5 module and APC 3.1.8 PHP opcode cache - runs on the front-end machine. A backend dataset (12GB on-disk) is generated using the Cloudstone benchmark [128]. The Faban driver [2] is used to simulate clients as usual.

Web Search - Web search engines get information through indexing, which is a process associating terabytes of data found from on-line resources to their domain names and HTML-based fields. An index serving node (ISN) of the distributed version of Nutch 1.2/Lucene 3.0.1 is analyzed with content crawled from the public internet, which has an index size of 2GB and data segment size of 23GB. It mimics real-world setups by making sure that the search index fits in memory, eliminating page faults and minimizing disk activity. Clients are simulated using the Faban driver and are configured to achieve the maximum search request rate while ensuring that 90% of all search queries complete in less than half a second.

### 3.2.2 SPEC CPU2006 benchmarks

The Standard Performance Evaluation Corporation (SPEC) CPU2006 suite are widely used in both industry and academia. This suite covers various aspects of system design, including CPU, memory systems, and compiler optimizations. SPEC CPU2006 is made of benchmarks representing real life applications rather than synthetic kernels or benchmarks. CPU2006 has 29 benchmarks, in which 12 are integer benchmarks and 17 are floating point benchmarks. All these benchmarks are single-threaded written in C, C++ and Fortran. In a simulation infrastructure with multicores, the multi-programmed workloads are formed by running one individual instance of one CPU2006 benchmark on one core.

### 3.2.3 Kernel summation

Kernel summation is a technique used to approximate the interactions between two sets of points in a high dimensional space. The need for fast kernel summation methods first appeared in computational physics, for example, computing the 3D Laplace potential (reciprocal distance kernel) and the heat potential (Gaussian kernel). Kernel summations are also fundamental to nonparametric statistics and machine learning tasks such as density estimation, regression, and classification [41, 44, 98, 121]. Linear inference methods such as support vector machines [130] and dimension reduction methods such as principal components analysis [98] can be efficiently generalized to non-linear methods by replacing inner products with kernel evaluations [11]. Problems in statistics and machine learning are often characterized by very high dimensional inputs.

There are numerous studies that have proposed scalable algorithms and high-performance implementations of fast kernel summation schemes such as treecodes [94][16], fast multipole methods [22][73], particle-mesh methods [120], Ewald sums [30], etc. These algorithms can scale to billions or trillions of points for problems in two or three dimensions. However, they do not scale to higher dimensions because they depend linearly or super-linearly on the dimension size.

# Chapter 4

# Data Locality Analysis and Micro-architectural Insights

The world is entering the era of big data and machine learning. A growing number of applications are working with very large data sets. Cloud computing is gaining popularity due to its ability to provide infrastructure, platform and software services to clients on a global scale. Using cloud services, clients reduce the cost and complexity of buying and managing the underlying hardware and software layers. Popular services like web search, data analytic and data mining typically work with big data sets that do not fit into top level caches. Popular DNN models have weights with size of tens to hundreds of MB [131]. Emerging RMS (recognition, mining, and synthesis) workloads have large working-set sizes greater than 16 MB on average [87].

Emerging applications typically work with significantly larger data sets and do not fit into the typical processor's top level (L1/L2) caches. With the emergence and growing relevance of several big-data application domains, analyzing and understanding the inherent patterns in the memory access streams of emerging applications is essential to design efficient memory hierarchies to optimize application performance. There have been several studies on characterizing the micro-architectural and memory system performance (cache miss rates, TLB miss rates, etc.) behavior of big data workloads [35, 38, 69] on modern computer systems. Prior arts have concluded that big-data workloads form a distinct workload class from desktop workloads, and current computer systems are inefficient to run those workloads. For example, Ferdman, et al. observe that simple hardware prefetching schemes in the current commercial computer systems do not work for cloud workloads [35]. However, there is no analysis or understanding of why hardware prefetching schemes do not work, and what micro-architectural improvements can be made to increase memory performance efficiency. Jaleel, et al. notice that small L2 caches degrade the performance of server workloads whose working set size is a few multiples (e.g. 2-4x) larger than the L2 cache capacity [51], and hence advocate for large L2 caches and relaxing cache inclusiveness.

In this chapter<sup>1</sup>, CloudSuite is taken as an example of modern scale-out workloads to present a detailed analysis of memory access pattern. This work focuses particularly on the behavior of memory accesses at the last-level cache and beyond. Spatial and temporal data locality of CloudSuite are computed to understand what is the reason that prevents certain prefetching schemes from improving CloudSuite performance, how would large caches help increase prefetch accuracy and coverage, and how to efficiently manage cache resources based on the data locality.

<sup>&</sup>lt;sup>1</sup>Contents of this chapter was previously published at the International Symposium on Performance Analysis of Systems and Software (ISPASS) in 2017 [140]. I am the principle author of this work.

### 4.1 Experimental Setup

| Table $4.1$ : S | System | Configuration |

|-----------------|--------|---------------|

|-----------------|--------|---------------|

| Processor   | 16 cores,                                           |

|-------------|-----------------------------------------------------|

| L1 cache    | 64KB, 4-way associative, 64B cacheline, LRU         |

| L2 cache    | 256KB, 8-way associative, 64B cacheline, LRU,       |

| L3 cache    | 8MB, 8-way associative, 64B cacheline, LRU, 16 MSHR |

| Main Memory | DDR3_1600K, 4 channels, 1 rank/channel              |

| Benchmarks      | Simulation length      | LLC accesses | LLC misses |

|-----------------|------------------------|--------------|------------|

| Data Serving    | 4 billion instructions | 36,134,150   | 14,993,597 |

| MapReduce       | 4 billion instructions | 38,119,693   | 16,644,104 |

| SAT Solver      | 4 billion instructions | 33,271,637   | 23,254,707 |

| Web Frontend    | 4 billion instructions | 10,311,403   | 2,277,452  |

| Web Search      | 4 billion instructions | 22,613,857   | 3,830,574  |

| Media Streaming | 4 billion instructions | 65,596,871   | 7,303,085  |

| mcf             | 1 billion instructions | 79,490,811   | 47,682,507 |

| bwaves          | 1 billion instructions | 23,176,132   | 22,677,841 |

| tonto           | 1 billion instructions | 158,098      | 35,737     |

Table 4.2: Workload characteristics

A multicore system is configured with private L1 and L2 caches, and a shared last level cache (LLC). Detailed system configuration is listed in Table 4.1. The simulation infrastructure collects the program counter of each instruction that triggers the LLC access, as well as the corresponding physical memory access address, access type (e.g., Load/Store/Eviction), and the interinstruction distance information of the LLC accesses. Six applications from the CloudSuite and three SPEC CPU2006 benchmarks with most LLC activity are chosen to illustrate differences between address patterns in SPEC workloads and CloudSuite. The representative phases of these workloads are captured and are used to generate LLC access traces with our tracing infrastructure. Table 4.2 summarizes the simulation intervals as well as the number of LLC accesses and LLC misses of each workload.

### 4.1.1 Temporal locality profile