# <u>Inf</u>inity Stream: Portable and Programmer-Friendly <u>In-/Near-Memory Fusion</u>

Zhengrong Wang seanzw@cs.ucla.edu UCLA, USA Christopher Liu chrisliu@cs.ucla.edu UCLA, USA

Aman Arora aman.kbm@utexas.edu UT Austin, USA

Lizy John ljohn@ece.utexas.edu UT Austin, USA Tony Nowatzki tjn@cs.ucla.edu UCLA, USA

#### **ABSTRACT**

In-memory computing with large last-level caches is promising to dramatically alleviate data movement bottlenecks and expose massive bitline-level parallelization opportunities. However, key challenges from its unique execution model remain unsolved: automated parallelization, transparently orchestrating data transposition/alignment/broadcast for bit-serial logic, and mixing in-/nearmemory computing. Most importantly, the solution should be programmer friendly and portable across platforms.

Our key innovation is an execution model and intermediate representation (IR) that enables hybrid CPU-core, in-memory, and nearmemory processing. Our IR is the tensor dataflow graph (tDFG), which is a unified representation of in-memory and near-memory computation. The tDFG exposes tensor-data structure information so that the hardware and runtime can automatically orchestrate data management for bit-serial execution, including runtime data layout transformations. To enable microarchitecture portability, we use a two-phase, JIT-based compilation approach to dynamically lower the tDFG to in-memory commands.

Our design, infinity stream, is evaluated on a cycle-accurate simulator. Across data-processing workloads with fp32, it achieves 2.6× speedup and 75% traffic reduction over a state-of-the-art nearmemory computing technique, with 2.4× energy efficiency.

## **CCS CONCEPTS**

$\bullet \ Computer \ systems \ organization \rightarrow Parallel \ architectures.$

#### **KEYWORDS**

Stream-Based ISAs, Programmer-Transparent Acceleration, In-Memory Computing, Near-Memory Computing

#### **ACM Reference Format:**

Zhengrong Wang, Christopher Liu, Aman Arora, Lizy John, and Tony Nowatzki. 2023. Infinity Stream: Portable and Programmer-Friendly In-Near-Memory Fusion. In Proceedings of the 28th ACM International Conference on Architectural Support for Programming Languages and Operating Systems, Volume 3 (ASPLOS '23), March 25–29, 2023, Vancouver, BC, Canada. ACM, New York, NY, USA, 17 pages. https://doi.org/10.1145/3582016.3582032

This work is licensed under a Creative Commons Attribution 4.0 International License.

ASPLOS '23, March 25–29, 2023, Vancouver, BC, Canada © 2023 Copyright held by the owner/author(s). ACM ISBN 978-1-4503-9918-0/23/03. https://doi.org/10.1145/3582016.3582032

## 1 INTRODUCTION

As multicore systems scale, growing data movement bottlenecks incentivize a memory-centric paradigm over the traditional corecentric paradigm. One realization of this is *near-memory computing*, where specialized hardware is added near memory banks to decouple computation from core pipelines and reduce communication demand. An alternative is *in-memory computing*, which augments memory arrays with the ability to perform simple computations at massive parallelism.

While in-memory computing has been applied at different hierarchy levels and technologies, the trend of incorporating extremely-large L3 caches has made the proposition of in-SRAM computation quite attractive. For example, the latest AMD EPYCs have >100MB of L3, which would translate to multiple millions of bitwise processing elements. As prior work has shown, bit-serial SRAM [32] has a computation density that is significantly higher than possible on SIMD vector units, and the energy benefits are substantial [17].

But there are still barriers to broad adoption. An ideal in-memory system would be as programmer-transparent as possible, be compatible with existing core-centric and near-data execution without adding much overhead, and also preserve program compatibility with future microarchitectures. No existing in-memory system has achieved all three due to the challenges of the unique paradigm:

- Transparent Orchestration: Bit-serial logic requires transposing large arrays, managing on-chip space, and enforcing bitline alignment. A suitable data layout, tiling, and explicit reuse are critical to reducing data traffic. Also, distributing computation to bitlines requires massive vector parallelism. Ideally, this orchestration would be done without any programmer involvement.

- Fused In-/Near-Memory Computing: Sometimes it is better to split the work between in-/near-memory computing. E.g. an in-memory reduction to produce partial results, which are reduced to the final value by near-memory computing; or a phase with both irregular and regular data structures, where only the latter is suitable for in-memory. This requires a unified execution model and low-overhead hardware implementation.

- Program Portability: High-performance implementations require exploiting both low-level microarchitecture details and software parameters, but fixing them would prevent portability and compatibility.

Existing in-memory works have not fully addressed these, as they are either somewhat domain specific (e.g. [9, 15, 16]) or put a significant burden on programmers (e.g. [1, 17, 30]).

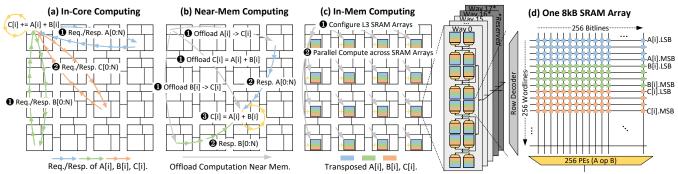

Figure 1: Overview of In-Core/Near-Mem/In-Mem Computing Paradigms

One source of inspiration is prior work on transparent near-memory called near-stream computing (NSC) [64], which augments the ISA with explicit abstractions for memory access patterns (called streams) and associated computation. In NSC, streams are offloaded to execute near-L3 when there is little locality in private caches. However, streams do not convey enough information and semantics for in-memory computing. They are inherently sequential, they lack information about data size and reuse which are needed to decide the best layout and tiling, and they also lack the necessary information to guarantee bitline alignment between data structures.

To solve this problem, our insight is that the portions of work-loads that can benefit from in-memory computation have very simple parallelism and reuse patterns that can be analyzed perfectly: generally affine access to multidimensional tensors. This information is sufficient to determine an optimized data layout and tiling, as well as for generating array-level data-movement commands to exploit reuse. Thus, our approach is to make parallel tensor access and relative memory alignment to be first-class primitives of program execution. The augmented program representation is called a *tensor dataflow graph* (tDFG). To first order, each tensor element is mapped to a bitline, and the dataflow instructions are mapped to in-memory commands.

Further, the tDFG is a unified abstraction for near-data and inmemory, as it defines the semantics when near-data streams have dependencies on in-memory tensor operations, and vice versa. For example, a load stream may broadcast the CNN weights to all bitlines (stream to tensor), or a reduction stream can execute near L3 banks to collect partial results from each SRAM (tensor to stream).

Finally, to enable portable binaries, we adopt a two-phase compilation approach. The tDFG serves as the compilers' intermediate representation (IR) and the program representation, and in-memory commands for SRAMs are generated by dynamic compilation of the tDFG. This enables the binary to be independent of microarchitecture, and for tensor programs to take advantage of runtime constants (tensor size/shape). Any difficult analysis happens while generating the optimized tDFG, thus lowering is fast.

Our overall approach is called *infinity stream*, which transparently and flexibly enables offloading to either in-/near-memory, fusing these paradigms. We implement our framework using LLVM and a custom dynamic compiler, and evaluate with gem5 [45]. For data-parallel workloads with in-memory phases using fp32, using a 64-core system with 128MB L3, infinity stream achieves 2.6× speedup and 75% traffic reduction over near-memory only [64] with 2.4× energy efficiency, and 5.1× (up to 8.9×) speedup over a

high-performance multicore. Specifically, our contributions are:

- Execution model for fused and general in-/near-memory computing, with automated data-layout transformations.

- In-memory compiler from plain-C, with optimizations for parallelism and data movement, enabling a programmer-friendly interface to efficient in-/near-memory execution.

- tDFG abstraction and ISA with μarch/runtime/JIT support for enabling portable in-memory execution.

- Quantifying the benefits of in-memory vs near-memory for bit-serial SRAM acceleration.

**Paper Organization:**  $\S 2$  gives background on in-/near-memory and overviews our approach, followed by the execution model and tDFG IR in  $\S 3$ .  $\S 4$  details the runtime and dynamic compilation, with the  $\mu$ arch in  $\S 5$  and limitations in  $\S 6$ . Methodology and evaluation are in  $\S 7$  and  $\S 8$ , and related work is in  $\S 9$ .

## 2 BACKGROUND AND OVERVIEW

Here we overview the three computing paradigms with a simple vector addition example. This characterizes in-memory computing and its challenges, which motivate this work.

## 2.1 Near-Memory Computing

Conventional systems adopt a core-centric view: all computation is centralized in the core, with data fetched from the memory subsystem. Fig 1(a) shows a tiled multi-core system. Each tile contains a core with a private L1/L2 and a shared L3 cache bank, and is connected by a mesh network-on-chip (NoC). To perform C[i]=A[i]+B[i], the core issues multiple requests to fetch A[i] and B[i], as well as writing back C[i]. Vectorization and multi-threading can be used to exploit the massive data parallelism in this example. One major overhead here is the unnecessary data movement, as all three arrays A[], B[] and C[] have no reuse at all. Techniques like prefetching and cache bypassing can only partially help, as the data movement is inevitable and incurs a high energy cost. Such overheads are only going to be more severe as the system scales up and the data grows.

Near-Memory Computing: To fundamentally eliminate unnecessary data movement, near-memory computing moves computation closer to the data, and has been applied in many contexts: e.g. near on-chip SRAM [53, 64], within the NoC [28, 56], near memory controller [3, 14, 44]. They also offload computation at different granularities from coarse-grained kernel-level [5, 31, 33, 42, 68, 73] to fine-grained short instruction sequences [3, 28, 56].

Near-Stream Computing: For the near-memory computing baseline, we use near-stream computing [64], which offloads long-term memory accesses (i.e. streams) with computations near the L3 cache. In Fig 1(b), the memory accesses are decoupled into three streams A[i], B[i], C[i], and offloaded to the shared L3 banks where the data resides. Stream A[i] and B[i] directly forward their data to stream C[i]. Stream C[i] coordinates with the remote CPU core to perform SIMD ops on a spare thread, and then writes directly to L3. This significantly reduces the data traffic and control overheads.

## 2.2 Bit-Serial In-Cache Computing

Near-L3 approaches still read the data out from the L3 SRAM arrays, hence are still bound by the L3 cache's bandwidth. To fully unlock the massive potential data parallelism, in-memory computing moves the computation *inside* SRAM arrays. For this work, we assume the same compute SRAM technology as Neural Cache [15].

In Fig 1(c), SRAM arrays are configured to add A[i] and B[i] in *parallel* and directly write back to C[i], with no sequential reads and writes at all. Fig 1(d) demonstrates how in-memory computing works in one 8kB SRAM array with 256 wordlines (row) and 256 bitlines (column). Specifically, it requires the data being transposed and bit-serial logic for computation.

**Transposed Data Layout:** In Fig 1(d), array elements (4 bits each) are transposed from a horizontal layout across columns to a vertical layout on the same column. E.g. the least significant bit (LSB) of A[0] is stored in the cell indexed by wordline 0 and bitline 0, and the most significant bit (MSB) of A[0] by wordline 3 and bitline 0.

**Bit-Serial Compute:** In-memory computing leverages bit-serial logic to compute the result. This requires operands to be aligned in the same column. In the example in Fig 1(d), A[i], B[i], and C[i] are all placed in the same bitline. To start the computation, we activate the wordlines of A[i].LSB and B[i].LSB at the same time, and the 256 PEs perform the bit operation on the sensed bit (e.g. AND for carry, XOR for addition). The PEs have cells holding intermediate results (e.g. carry of addition). The result bit is then written back to C[i].LSB by activating wordline 8 with the write signal. This process repeats to compute the result one bit at a time (hence "bit-serial"). It takes O(n) cycles to perform integer addition and  $O(n^2)$  for integer multiplication, where n is the data type width. However, this is amortized by the massive parallelism it provides.

**Max System Speedup:** Assuming a 64-core system with 16-way 2MB L3 banks (total 128MB) and 16 256×256 SRAM arrays/way, the peak throughput of int32 addition is:

$$T = N_{bank} \times N_{way} \times N_{array/way} \times N_{bitline}/Latency^{1}$$

= 64 × 16 × 16 × 256/32 = 131072 ops/cycle (1)

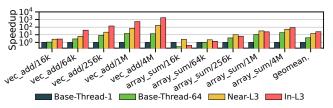

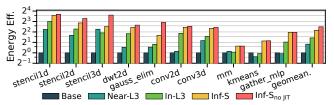

Assuming each baseline core can issue one 512-bit vector op per cycle ( $64 \times 16 = 1024$  ops/cycle), in-memory provides  $128 \times$  peak speedup. Fig 2 shows the speedup of two microbenchmarks with various input sizes on the baseline (AVX-512 and 1 or 64 OpenMP threads), near-L3, and in-L3 computing using bit-serial logic. We assume data is cached in L3 and already transposed for in-memory computing. in-L3 computing usually favors larger input sizes as they amortize the overhead of bit-serial operation. Despite this,

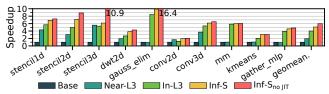

Figure 2: Speedup of Different Paradigms (Fp32)

in-L3 achieves the best performance for vec\_add across all input sizes. With 4M elements, it achieves 21× over Near-L3, making it a promising approach to exploit the available data parallelism.

## 2.3 Infinity Stream Approach Overview

We overview our approach by revisiting each of our driving requirements from the introduction.

**Automated Orchestration:** The data layout and movement orchestration – i.e. allocation, alignment, transposition, and tiling – are critical to the performance and applicability of in-memory computing. Thus, the system must automate this management and ease integration with conventional code. The key challenge is expressing sufficient information to the hardware and software runtime.

Our approach: We develop a program representation called the tensor dataflow graph (tDFG). The tDFG operates over tensors with explicit data-parallel semantics, and represents inter-data structure alignment with the concept of a global lattice space. Reuse can be determined precisely, and the tDFG can be annotated with hints about optimal tiling patterns. The tDFG is embedded as an extension to a traditional ISA, and gives the runtime sufficient information to make good decisions.

**Fused In-/Near-Memory Computing:** As suggested by Fig 2, in-memory struggles with small input sizes. Also, many code patterns like irregular control and memory (e.g. A[B[i]]) are only potentially suitable for *near*-memory. This motivates both a runtime selection between in-/near-memory computing, and a fused in-/near-memory paradigm.

Our approach: The tDFG can express both in-memory and near-memory opportunities in a unified representation. This generalizes the near-data approach from near-stream computing [64]. At runtime, the system decides the offload target (in-/near-memory) based on data size and access behavior. One key hardware feature is to integrate the transposed data layout with the coherence protocol to allow data communication between the two paradigms.

**Portability:** High-performance in-memory code requires exploiting both low-level hardware details (e.g. # of bitlines/array, SRAM-level instructions) and runtime values, e.g. array dimensions, compute constants. Thus, it is difficult for a single low-level binary to be compatible with all software parameters and future microarchitectures without sacrificing performance.

Our approach: We take a just-in-time (JIT) approach, with the tDFG playing a similar role to PTX virtual assembly for CUDA GPUs. A JIT runtime is in charge of quickly lowering the tDFG "virtual" ISA into in-memory computing commands and managing the transposed data layout. This requires carefully splitting the job between the compiler and the runtime to maintain compatibility while keeping JIT overheads reasonable.

$<sup>^1\</sup>mbox{We}$  adopt the integer addition from [17]. System params in §7. See In-/Near-Memory Computing [18] for more details, and §9 for related works.

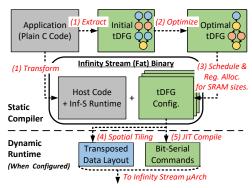

Figure 3: Infinity Stream Workflow Overview

**Programmability:** Ideally, the system should be easy to program, without programmers writing multiple code versions, worrying about data orchestration, and switching between paradigms. This requires a unified compiler and ISA abstraction, as well as a flexible runtime library and microarchitecture support.

*Our approach:* The tDFG is constructed purely by the compiler using plain C code. The algorithm and program transformations (e.g. inner vs. outer product) can of course affect the performance, so we discuss programming implications in §3.5. Overall, infinity stream requires only minimal programmer intervention.

Infinity Stream Workflow Overview: Fig 3 summarizes the overall workflow: our static compiler first extracts an initial tDFG from plain C code and optimizes it for compute reuse and less data traffic. The optimal tDFG is scheduled for common SRAM sizes (we use  $256 \times 256$  and  $512 \times 512$ ). This generates a fat binary with multiple tDFG configurations, which reduces the complexity of JIT compilation. At runtime, when an infinity stream region is configured, the runtime dynamically decides the transposed data layout with tiling based on the data size and hardware parameters. The matched version of tDFG is JIT lowered into bit-serial commands. The infinity stream  $\mu$ arch transposes the data and executes the commands to perform in-memory computing.

## 3 INFINITY STREAM ABSTRACTION

This section shows how the proposed abstraction captures the unique properties of in-memory computing to enable helpful optimizations while simplifying programming complexity.

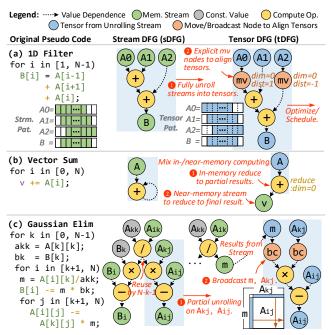

#### 3.1 Stream Dataflow Graph

We first extract the stream dataflow graph (sDFG) from the program, which embeds memory access patterns as *streams* with associated near-stream computations. We leverage the sDFG as the foundation and later extend it to support in-memory computing.

**Stream:** The compiler decouples access patterns into streams. E.g. Fig 4(a) contains three load streams A[i-1], A[i], A[i+1], and one store stream B[i], with linear access patterns. Streams may be extracted from outer loops if the access pattern is supported. Irregular access patterns (e.g. A[B[i]] and p=p->next) are also streams but are inefficient for pure in-memory computing.

**Near-Stream Computation:** Computation can also be associated with streams. E.g. in Fig 4(b) the reduction is associated with stream A[i]. Although the operation is applied to all elements, streams still

Figure 4: Examples of Infinity Stream Abstractions

| tDFG Node                                                                                                 | Lattice Space Representation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Semantic                                                                                                                                    |

|-----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| A = tensor( ptr <sub>data</sub> , p <sub>0</sub> , q <sub>0</sub> , p <sub>N-1</sub> , q <sub>N-1</sub> ) | $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | A N dimension <i>hyperrectangle</i><br>set of <b>data elements</b> in<br>lattice space.                                                     |

| $A_{o} = cmp(A_{0} \cdots A_{M})$ $f,$ $A_{0}, \dots A_{M})$                                              | A <sub>o</sub> =∩A <sub>i</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Apply an element-wise f(A <sub>o</sub> ) to the intersection of input tensors.  Assume no inter-elem. order.  @ret: a tensor A <sub>o</sub> |

| A <sub>o</sub> = mv(<br>A,<br>dim, dist)mv                                                                | 1 2 3 4 mv 1 2 3 4 dim=0<br>5 6 7 8 mv 5 6 7 8 dim=0<br>9 100 112 9 100 112 dist=1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Move the input tensor <b>A</b> by <b>dist</b> in dimension <b>dim</b> . @ret: a tensor <b>A</b> <sub>o</sub>                                |

| A <sub>o</sub> = bc(<br>A, count,<br>dim, dist)bc                                                         | 1234 bc 1234 count=4 dim=1 1234 dist=0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Broadcast tensor <b>A count</b> times in dimension <b>dim</b> with offset <b>dist</b> .  @ret: a tensor <b>A</b> <sub>o</sub>               |

| v A = strm(S) acc_pat)                                                                                    | $ \begin{array}{c c} & Access \ \textit{Pattern}: \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ &$ | Sequentially accesses the array using the access pattern. @ret: normal values v   a tensor A                                                |

| C = const(<br>c)                                                                                          | value c broadcasted to all lattice cells.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | An infinite tensor <b>C</b> with compile-/run-time constant <b>c</b> at <b>all lattice cells</b> .                                          |

Figure 5: tDFG Node Semantics

implicitly define the access order and preserve sequential semantics. In hardware, each stream (and associated computation) can be independently moved near the L3 if more locality there.

**Stream Dataflow Graph:** Streams and near-stream computations form the stream DFG. Streams can have dependences: data from the outer loop can be reused by the inner loop, e.g. in Fig 4(c) where the value m is reused (N-k-1) times.

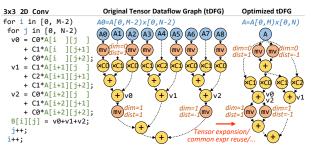

#### 3.2 Tensor Dataflow Graph

**Intuition:** In-memory computing requires unrolling computation across all bitlines. Inspired by this observation, if the domain of the stream is a hyperrectangle (i.e. *N*-dimensional rectangle) of the data structure, we can fully unroll the stream into a *tensor*. We can then reformulate the computation as a dataflow graph where

the operands are tensors; we call this the tensor DFG (tDFG). Fig 4 shows three example tDFGs, and Fig 5 summarizes all types of tDFG nodes. We now define the key concepts and semantics of the tDFG.

Global Lattice Space: A key feature of the tDFG is the ability to reason about the relative location of different tensors in memory, so that data can be aligned at the bitline level. To enable abstract reasoning about relative locality, we introduce a global lattice space to the tDFG. All tDFG tensors are positioned on an *N*-dimension global lattice space (its dimensionality is that of the data structure with the highest dimension), shown as the dashed grid in Fig 5. Each lattice cell can hold an arbitrary number of data elements. At runtime, cells are mapped to physical locations, e.g. SRAM bitlines. More importantly, the lattice space serves as a homogeneous coordinate system to abstract away the complex underlying hardware hierarchy, including bitlines, SRAM arrays, banks, NoC, etc. This helps keep the tDFG abstraction portable across platforms.

**Tensor:** As in Fig 5, a tDFG tensor is a hyperrectangle set of data in the lattice space, denoted by  $[p_0, q_0) \times ... \times [p_{N-1}, q_{N-1})$  where  $p_i$  and  $q_i$  are the start and end coordinate in dimension i. Each data element of a tensor resides in its own lattice cell. An N dimensional array is by itself a tensor with  $p_i = 0$ ,  $q_i = S_i$  where  $S_i$  is the array size on dimension i. Unlike streams, tensors do not imply a temporal sequential order but are fully expanded in the lattice space.

Compute with Tensors: A compute node takes one or more input tensors, applies the computation to a domain which is the intersecting hyperrectangle (see Fig 5), and produces an output tensor. The tDFG uses a static single-assignment form (SSA), i.e. nodes always produce a new tensor without overwriting existing ones. There are two key characteristics of tensor computation:

- Data Parallelism: Since tensors are fully unrolled, the tDFG does not assume an elementwise order within one tensor computation, exposing massive data parallelism.

- Data Alignment: Tensor computation requires operand elements from different tensors to be exactly aligned within the same lattice cell. This captures the data alignment requirement for in-memory computing.

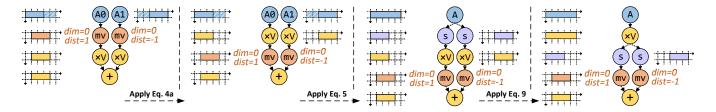

**Explicit Tensor Alignment:** We introduce two types of node in the tDFG to facilitate explicit tensor alignment, which is crucial to optimize and compile data movement for in-memory computing:

- Move: A move node (mv) in Fig 5 shifts a tensor along a dimension by a certain distance. E.g. in Fig 4(a), tensor A[0,N-2) is moved to the right by 1 to align with A[1,N-1).

- **Broadcast:** To capture reuse spatially, a broadcast node (bc) in Fig 5 broadcasts a small reused tensor along the reuse dimension to align with the larger tensor. In Fig 4(c) A[k,k+1)x[k+1,N) is broadcast downwards to align with A[k+1,N)x[k+1,N).

Global Bounding Hyperrectangle: Due to the finite hardware resources, not every lattice cell has a valid physical location. we define the global bounding hyperrectangle as the minimal one that contains all involved data structures. semantically, data elements outside the bounding hyperrectangle have undefined values, so data moved or broadcasted outside is discarded. For now, we implicitly assume all data structures are aligned to the origin, but this can be relaxed to placing the array anywhere in the lattice.

Optimizing tDFG: We leverage equality graphs (e-graphs) [47, 48]

Figure 6: Example of Optimized tDFG

to search for an optimized tDFG. E-graphs are a representation of all possible re-writes to a graph in a compact form, which leverages equality relationships between different re-writes. To construct an e-graph for our case, we start from the initial tDFG, then repeatedly grow the e-graph by applying re-writes and maintaining equivalence points between them. The final tDFG selection is based on architecture-informed cost metrics (e.g. estimated latency of move vs. compute node), and can be exhaustive or terminated early to reduce compile time. Fig 6 shows the initial and optimized tDFG for Fig 4(c). Besides the basic associative, commutative, and distributive rules, two transformations are widely applicable (see the Appendix for a full list of transformation rules):

- **Tensor Expansion**: We can merge two mvs with same distance and dimension but on slightly different patterns. In Fig 6,  $A_0:[0,M-2)\times[0,N-2)$  and  $A_3:[1,M-1)\times[0,N-2)$  are both shifted to the right by 1, and can be merged into one mv on the expanded tensor  $[0,M-1)\times[0,N-2)$ .

- **Reuse Common Comp.**: We can also reuse common computations. In Fig 6, instead of multiplying by *C*0 four times, we can reuse the result by shifting it to where it is needed in the lattice.

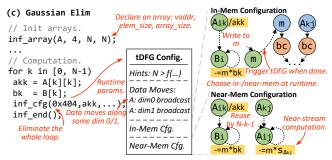

# 3.3 Hybrid In-/Near- Memory

tDFG is also general and flexible to support hybrid in/near memory execution by embedding streams.

**Embedding Streams in tDFG:** Some streams/ops in the tDFG are not unrolled into tensors, e.g. alias, non-hyperrectangle accesses, etc. Keeping streams in the tDFG enables data to be read or written in a strided affine pattern or an indirect pattern, providing a better setup for tensor computation (e.g. a stream performs an indirect access and lays out the data in a tensor format). We allow up to three dimensions for affine access and dependent one-level indirect access (see the access pattern in Fig 5). A stream node can produce:

- Normal Values: Load and reduce streams generate normal values (non-tensor) consumed by the core or other streams. E.g. the reduction in Fig 4(b) is split into two nodes: a tensor compute node to perform partial in-memory reduction, and a stream node to perform the final reduction, as in-memory computing is inefficient for the final rounds.

- Tensor Values: Store streams produce a new tensor with the

bounding hyperrectangle of all touched lattice cells. Semantically, this can be as large as the entire accessed array, e.g. an

indirect stream updates a subset of the elements. However, in

implementation, this is just updating an existing tensor and does

not allocate a new one. In Fig 4(c), stream B<sub>i</sub> is not unrolled due

to low parallelism, and stream m writes the division result into

a tensor m, which is later consumed by in-memory computing.

Figure 7: Example of Compiled Infinity Stream Program

**Supporting Irregularity:** Hybrid in-/near-memory execution enables infinity stream to handle some forms of irregularity, i.e. streams in tDFG can have irregular access patterns (e.g. A[B[i]]). For example, in kmeans, in-memory computes the closest centroid for each point using tensor operations, while near-memory performs the indirect update to recalculate centroids' coordinates. For future work, the tDFG can also be extended with control flow and predication to handle control irregularity.

## 3.4 ISA Interface

Both the sDFG and tDFG for each relevant program region are encoded in the binary, to enable a dynamic choice between nearmemory and in-memory respectively. Fig 7 shows the compiled Fig 4(c) with both DFGs and data layout hints.

Infinity Stream Configuration: The inf\_cfg instruction marks the beginning of infinity stream regions, and passes in the runtime parameters (e.g. constant values). This triggers the runtime library to read in the configuration and configure the microarchitecture (details in §4 and §5). As in prior work [64], near-stream computations are compiled into conventional functions in the native ISA. A pointer to this function is stored in the sDFG.

Layout Hints for Tiling: We add layout hints into the configuration to help the runtime quickly make good decisions about tiling: e.g. which dimensions the array would be shifted along (favoring tiling along those dimensions), as well as which arrays are used for the same computation (and should be bitline-aligned). The compiler generates the layout hints by analyzing the tDFG's data movement patterns. The runtime also requires the array sizes, which are passed in using the inf\_array API. Fig 7 demonstrates using inf\_array to declare a 2D array A[N][N], where the infinity stream configuration defines that array A is broadcast in both dimensions. The runtime combines this information and picks a suitable data layout to reduce the traffic (see §4.1). Currently, we manually insert inf\_array calls in the initialization phase.

tDFG Backend Compilation: To generate a tDFG configuration, the backend compiler serializes the tDFG and allocates values to wordlines (once for each SRAM array size in the fat binary). In this work we use a straightforward approach of scheduling instructions in topological order, and using a local register allocation scheme [4]. Though there are few effective registers (e.g. 8 32-bit registers in a 256-wordline SRAM array), no register spilling was observed in the studied workloads. Fusing multiple physical SRAM arrays into a larger virtual array with more registers is possible, but left for future work.

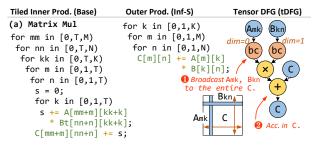

Figure 8: Programming GEMM for Infinity Stream

Figure 9: Moving a Tensor in Tiled Layout (View in Color)

## 3.5 Programming Infinity Stream

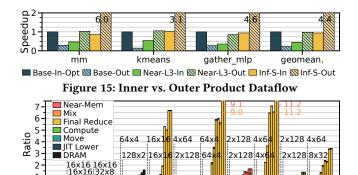

Due to its special execution model, programmers face different trade-offs when programming an in-memory system, with tiling and dataflow being the two major design choices.

**Tiling:** Since in-L3 computing flattens the memory hierarchy, it becomes unnecessary to tile for L1/L2 caches at the programming interface. The runtime will handle the tiling across SRAM arrays using microarchitecture support. E.g., Fig 8 shows the baseline 2-level tiled code for matrix multiplication mm, while infinity stream's implementation has no tiling with only 3 loop levels.

Inner vs. Outer Product: Another critical design choice is the dataflow. In-core computing usually favors inner product as it accumulates the result in the register (see Fig 8). However, as in Fig 2, in-memory computing does not handle reduction well as the data parallelism is halved after each round of reduction, and prefers outer product to convert the reduction to element-wise operations. In Fig 8, during each round of k, one column of A[] and one row of B[] is broadcast to the entire C[], followed by multiplication and accumulation. We evaluate both dataflow choices in §8.

**Best Practice:** Programmers should choose outer product or a similar dataflow that exposes more parallelism for inner loops and move reduction to outer loops. Also, there is no need to tile for private caches as in-memory computing is performed at L3. As in standard practice, programmers should still tile for L3 to provide a suitable working set for in-memory computing.

#### 4 RUNTIME SUPPORT

The tDFG is neutral to hardware details and input sizes to maintain compatibility. Instead, a runtime library manages the transposed data layout, lowers the tDFG into in-memory commands, and decides between in-/near-memory computing, described as follows.

#### 4.1 Transposed Data Layout

The transposed data layout is left to runtime as it requires information that is usually unavailable at compile time, e.g. input sizes, SRAM array sizes, NoC bandwidth, etc.

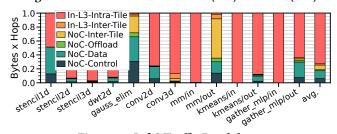

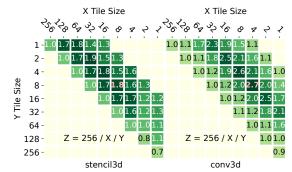

A trivial data layout would treat the data structure as a 1D array and map elements to contiguous bitlines. However, tensors are often shifted/broadcast along higher dimensions. Therefore, to reduce data traffic across SRAM arrays, the data layout within an SRAM is modified through tiling. Here, a *tile* is defined by the data dimensions mapped to one SRAM array. In Fig 9 we consider a 4-bit-wide SRAM array, where a 4x4 2D software array is split into 4 2x2 tiles, and mapped to SRAM arrays (some SRAMs belong to ways reserved for conventional cache). We only transform the data layout through tiling at the SRAM array level, as it captures most of the traffic reduction benefits, and keeps the mapping between physical address and bitlines simple. Applying further data-layout tiling at a coarser level could further reduce data traffic.

**Tiling Constraints:** Assume an N-dimensional  $S_0 \times ... \times S_{N-1}$  array with L elements per cache line, B bitlines per SRAM array and W SRAM arrays per L3 bank used for in-memory computing. The tile size  $T_0 \times ... \times T_{N-1}$  must ensure that:

- (1)  $\prod_{i=0}^{N-1} T_i = B$ : Each tile occupies all bitlines in one SRAM array. This simplifies the logic for intra-tile data movement.

- (2)  $T_0 \times W \mod L = 0$ : For dimension 0 (continuous in address space), tiled elements at each L3 bank ( $T_0 \times W$ ) aligns with elements per cache line (L). This ensures that each line is mapped to only one L3 bank.

The runtime gets the array's element size and shape from the inf\_array API, and searches for a valid tile size meeting the constraints. If none is found, the array is not transposed and in-memory computing is disabled. Notice that the array size is not required to align to tile size; boundary tiles with unused bitlines require special handling (see §4.2 and §5). In addition, it checks that the array's innermost dimension aligns to the cache line ( $S_0 \mod L = 0$ ). Along with constraint 2, this guarantees a transposed cache line is not split across L3 banks, and is still accessible by normal requests (with longer latency to transpose back, see §5). This rarely fails for large arrays, as they are often padded for cache line alignment.

When multiple arrays are used by the same computation, e.g. the input and output array of 2D convolution, the runtime picks one primary array (the output or the reduced array) and uses its tile size for others. Using the same tile sizes eases the complexity to align tensors at runtime.

Tiling Heuristics: The runtime picks one valid tile size using hints in the configuration. Shifts favor a close-to-square tile size, as it keeps most traffic within the same tile. For reduction, a larger tile size on the reduced dimension allows more rounds of in-memory reduction. Broadcast reads favors a smaller innermost tile size if it can spread one row to more L3 banks to avoid the hotspot. When tensors are used for multiple kinds of data movement, we prioritize by the order of reduction, shift, and broadcast, as reduction is usually more expensive due to low compute intensity, while broadcast is inexpensive, as it can reuse the read data. The runtime can pick the best data layout for each program phase. Our heuristic is within 2% of an oracle configuration (see §8).

#### 4.2 JIT Lowering tDFG

The runtime also lowers the tDFG into in-memory commands. In Fig 9, an example mv node (right shift columns [0, 3) by 1) is lowered through the following steps.

#### **Algorithm 1:** Decompose Tensor

```

Input: A N-dim tensor A = [p_0, q_0) \times ... \times [p_{N-1}, q_{N-1}) where p_i < q_i

Input: A list of tile size of each dim ts = [t_0, ..., t_{N-1}]

Result: A list of decomposed tensors ret initialized as []

1 if N > 0 then // Decompose dimension 0

head ____ middle ____

a \leftarrow \lfloor \frac{p_0}{t_0} \rfloor \times t_0, b \leftarrow \lfloor \frac{p_0 + t_0 - 1}{t_0} \rfloor \times t_0 \text{ // Align } p_0 \text{ to tile boundary } c \leftarrow \lfloor \frac{q_0}{t_0} \rfloor \times t_0, d \leftarrow \lfloor \frac{q_0 + t_0 - 1}{t_0} \rfloor \times t_0 \text{ // Align } q_0 \text{ to tile boundary } \text{ // Recursively decompose remaining dimensions}

rs \leftarrow \text{Decompose}([p_1, q_1) \times ... \times [p_{N-1}, q_{N-1}), [t_1, ..., t_{N-1}])

forall A' \leftarrow rs do // Construct final decomposed tensors

if b \le c then // a \le p_0 < b \le c \le q_0 < d

if a < p_0 then

ret += [p_0, b) \times A' // Head interval

10

if b < c then

11

ret += [b, c) \times A' // Possible middle interval

12

13

ret += [a, c) \times A' // p_0 aligns with a

if c < q_0 then

15

re\hat{t} += [c, q_0) \times A' // Add possible tail interval

16

else // a = c \le p_0 < q_0 < b = d

ret += [p_0, q_0) \times A' // Same tile, no decomposition

19 else // No more dimension to decompose

ret += A

```

**1. Tensor Decomposition:** As tensors may not align to the tile boundary (e.g. moving a subregion of the array), they are decomposed into smaller ones to separately handle those tiles at the boundary. Alg 1 recursively decomposes an N-D tensor along the tile boundary at each dimension. For the start and end position  $p_0, q_0$  of dimension 0, it identifies their respective tile boundaries [a, b), [c, d) such that  $p_0 \in [a, b), q_0 \in [c, d), \{a, b, c, d\} \mod t_0 \equiv 0$  (line 3-4). Depending on the relative positions of  $p_0$  and  $q_0$ , it decomposes the 1D tensor  $[p_0, q_0)$  into one to three new ones: additional subtensors for the head and/or tail if  $p_0$  and/or  $q_0$  do not align with the tile boundary. For multiple dimensions, we take the cross product of all decomposed tensors (line 8-18). When the tensor aligns with the tile boundary in every dimension, no decomposition is needed.

For example in Fig 9,  $A[0,4)\times[0,3)$  is decomposed into two subtensors  $A_L[0,4)\times[0,2)$  made of full tile 0 and 2, and  $A_R[0,4)\times[2,3)$  made of partial tile 1 and 3. Since dimension 0 is perfectly aligned, the original range  $[p_0=0,q_0=4)$  is kept (line 13). For dimension 1, the range  $[p_1=0,q_1=3)$  means the tail is not aligned  $(t_1=2\implies q_1\mod t_1\not\equiv 0)$ . Therefore dimension 1 is decomposed into  $[p_1=0,2)$  and  $[2,q_1=3)$ . The cross product between decomposed dimensions 0 and 1 yields two subtensors  $[0,4)\times[0,2)$  and  $[0,4)\times[2,3)$ .

2. Intra-/Inter-Tile Shifts: Alg 2 lowers a decomposed mv node into intra-/inter-tile shift commands. Each shift command takes five arguments: 1) a tensor A, 2) a shift dimension k, 3) a shift mask that selects the bitlines to shift, and 4,5) the inter-/intra-tile shift distances that indicate the direction and number of tiles/bitlines to shift (intra-tile shifts always have 0 inter-tile shift distance). Depending on whether the shift distance aligns with the tile boundary ( $d_{intra} == 0$ ), we may generate an inter-array shift command and optionally an extra intra-array shift command (line 5-12). Notice that not all shift commands will necessarily generate traffic, as the intersection of the shift mask and the tensor may be the empty set. Such shift commands are filtered out later (ommitted in Alg 2).

#### Algorithm 2: Compile mv to Shift Commands

```

Input: A N-dim tensor A = [p_0, q_0) \times ... \times [p_{N-1}, q_{N-1}) where p_i < q_i

Input: Tile size t_k of move dimension k and move distance d

Result: A list of shift commands ret initialized as []

\text{1} \quad d_{inter} \leftarrow \lfloor \frac{\text{abs}(d)}{t_k} \rfloor \text{ // Inter-tile shift distance}

2 \ d_{intra} \leftarrow abs(d) \ mod \ t_k \ // \ Intra-tile \ shift \ distance

3 \overline{d}_{intra} ← t_k – d_{intra} // Complement of d_{intra}

4 // Shift(tensor, dim, mask, inter_tile_dist, intra_tile_dist)

5 if d > 0 then // Shift forward

ret += Shift(A, k, [0, \overline{d}_{intra}), d_{inter}, d_{intra})

if d_{intra} > 0 then

ret += Shift(A, k, [\overline{d}_{intra}, t_K), d_{inter} + 1, -\overline{d}_{intra})

else if d < 0 then // Shift backward

10

if d_{intra} > 0 then

ret += Shift(A, k, [0, d_{intra}), -(d_{inter} + 1), \overline{d}_{intra})

ret \mathrel{+=} \mathsf{Shift}(A, k, [d_{intra}, t_K), -d_{inter}, -d_{intra})

12

```

As an example, in Fig 9, shifting  $A_L[0,4)x[0,2)$  to the right by one requires one intra-tile shift to move the column 0 (CMD 0, Alg 2 line 6), and one inter-tile shift to move the column 1 across the tile boundary (CMD 1, Alg 2 line 8). Each command has the bitline/tile pattern generated by intersecting the tensor with the shift mask. These patterns are applied to bitlines/tiles, specified using the start[:stride:count]+ format. E.g. CMD 1 has bitline pattern 1:2:2 and tile pattern 0:2:2, therefore shifts bitline 1, 3 of tile 0, 2 (red arrow). These patterns are expanded into masks by the hardware when executed (see §5). Activated wordlines are also encoded, but are omitted in Fig 9 for simplicity. Shift commands also have the bitline/tile distance to determine the destination bitline/tile. Similarly,  $A_R[0,4)x[2,3)$  is shifted to the right by one intra-tile shift (CMD 2, Alg 2 line 6), but requires no inter-tile shift (skipped Alg 2 line 8). The runtime ensures data is not shifted beyond the array boundary by checking the tensor size and the shift distance.

**3. Map to L3 Banks:** Some commands, e.g. those for boundary tiles, may be skipped by some banks. The runtime intersects the commands' tile pattern and the tiles mapped to each L3 bank. If the intersection is empty, the command can be skipped at that L3 bank. In Fig 9, since CMD 0 operates on tile 0 (mapped to L3 bank 0) and tile 1 (mapped to L3 bank 1), it is mapped to both L3 banks.

Other tDFG Nodes: Element-wise compute nodes do not move the data and can skip step 2, but still needs step 1 and 3 to handle the boundary tiles and to be mapped to L3 banks. The compute commands also encode the opcode and the wordlines of the operands and result. Reduction nodes are lowered into a sequence of interleaving compute and intra-tile shift commands to fully reduce each tile on the reduced dimension. Broadcast nodes are handled similarly to move nodes, with the broadcast destination encoded.

**Synchronization:** All commands are synchronous at L3 banks (i.e. do not issue until the previous one finished) except inter-tile shifts, which are considered finished when all data movement within the L3 bank *and* the inter-bank packets are injected into the NoC (but may before they arrive at the destination L3 bank). Therefore, the runtime inserts a sync command between an inter-tile shift command and the consuming command, which serves as a global memory barrier, ensuring that data movements before the sync command are visible to commands after the sync command. (i.e. arrived at the destination bitline). A sequence of pure intra-tile shift and compute commands require no synchronization.

**Reducing JIT Overheads:** Being on the critical path of offloading, JIT lowering can incur significant overheads. Thus, we co-design the software and hardware for JIT performance:

- **Division of labor:** The static compiler handles register allocation and scheduling (see §3.4), so the JIT compiler only needs to map the scheduled tDFG according to the tiled data layout and lower into bit-serial commands. This is possible by scheduling for common SRAM array sizes (256x256 and 512x512), forming a fat binary similar to CUDA. Note that our fat binary does not expose any microarchitecture beyond the SRAM array sizes, and we believe there will only be a small handful that are useful over many generations of hardware.

- Memoization: We reuse JIT results when the same tDFG is re-executed with the same parameters by adding a small hardware cache (see §5) for intermediate reuses and software memorization for longer-term reuses. This is particularly useful for iterative algorithms (e.g. stencils).

- Array dimension specialization: While our JIT compiler can handle higher dimensional arrays, we specialize for common 1-3D arrays by leveraging C++ templates. This enables the compiler to unroll the loop and eliminate expensive recursion (e.g. Alg 1 recursively decomposes the tensor according to the tile boundary).

With these optimizations, we reduced JIT lowering time by more than 1000×, and it takes 12% of overall runtime (see §8). We believe additional optimizations could further reduce the overhead, e.g.:

- Phase overlapping: We can overlap JIT compiling with the data preparing phase (to fetch and transpose data, see §5), or lowering for future regions as the core is waiting for the current region to finish.

- Hardware implementation: We can broadcast commands after step 2 to all L3 banks and let the hardware skip those not applied to its local tiles, eliminating step 3 (the most timeconsuming one as it is O(N<sub>bank</sub> × N<sub>cmd</sub>)) in software.

# 4.3 In-/Near-Memory Decision

The runtime also decides between in-/near-memory computing by evaluating the following condition:

$$\frac{N_{elem} \times N_{op}}{TP_{core}} > \Sigma_{i} Lat_{op_{i}} + N_{node} \times Lat_{JIT}$$

(2)

The LHS models the latency of a core at peak throughput, and the RHS captures the in-memory computing delay (first term, no  $N_{elem}$ , as computation is fully parallelized) and the JIT time (second term). The compiler generates aggregate information as hints in the configuration, e.g. # of each op, so that the runtime can make a quick decision without analyzing the tDFG. Other platform-specific parameters can be obtained by querying the hardware or profiling offline. This is just a basic and conservative heuristic (assuming peak core performance), but is sufficient for the studied workloads.

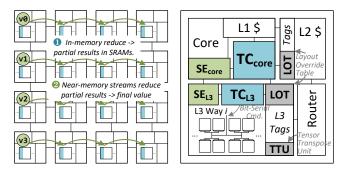

## 5 MICROARCHITECTURE EXTENSIONS

Fig 10 overviews infinity stream's microarchitecture, with stream engines ( $SE_{core}/SE_{L3}$ ) handling offloaded near-memory streams, layout override tables (LOT) recording transposed data layout, and tensor controllers ( $TC_{core}/TC_{L3}$ ) executing in-memory commands and synchronizing with the core.

Figure 10: Infinity Stream Microarchitecture

## 5.1 Near-Memory Computing

We adopt near-memory computing  $\mu$ arch support from NSC [64] to execute streams at the L3 stream engine (SE<sub>L3</sub>). Streams read/write data directly from L3 banks and forward operands to consuming streams without going back to the core for computing. Streams automatically migrate to the L3 bank where the next data is mapped, with coarse-grained flow control messages (i.e. sync every N cache lines between SE<sub>core</sub> and SE<sub>L3</sub>) to reduce coordination.

# 5.2 In-Memory Computing

During in-memory computing mode, the microarchitecture needs to manage the transposed data layout (LOT and  $TC_{core}$ ), execute the in-memory commands ( $TC_{L3}$ ), and synchronize with the core ( $TC_{core}$  and  $TC_{L3}$ ). We assume the SRAM arrays are enhanced to support bit-serial logic and shifts, as well as a buffered H tree to enable efficient broadcast, similar to [15, 17].

**Transposed Data Layout:** The layout override table (LOT, Table 1) tracks the transposed arrays initialized by the runtime (up to 3D, so higher-dim arrays should have some dimensions fused). It tracks the physical address, as the L2 and L3 caches are indexed by physical addresses. This requires the array to be contiguous in physical address space (with huge pages or special malloc functions). Directly mapping virtual addresses to bitlines is possible by extending the page table and TLB for transposed pages, but is beyond this work.

Map Physical Address ⇔ Bitlines: The LOT essentially overrides how physical addresses are mapped to SRAM arrays. For transposed data structures, the physical address is subtracted by base and divided by size to get the element index, which is used to find the containing tile and coordinates within that tile. Since tiles are mapped contiguously to SRAM arrays, it is straightforward to locate the actual bitline and wordlines. Reverse mapping from bitlines to physical addresses is similar.

**Prepare Transposed Data:** Before in-memory computing,  $TC_{core}$  prepares the data in transposed format by first issuing flush requests to the L3 cache controller to reserve the cache ways used for in-memory computing (we use 16 ways).

The trans field in LOT (initialized to 0) indicates whether the data is currently cached in transposed layout. If trans=0,  $TC_{core}$  offloads a load stream to fetch the data into transposed format, and sets trans=2 when finished. During this process,  $TC_{core}$  sets trans=1, and any core requests to that physical range is blocked. These load streams are executed in  $SE_{L3}$  to avoid the traffic overheads between L2 and L3. Our design uses a tensor transpose unit

Table 1: Layout Override Table (LOT)

| Field   | Bits | Description              | Field | Bits | Description             |

|---------|------|--------------------------|-------|------|-------------------------|

| base    | 48   | Base phys. addr.         | end   | 48   | End phys. addr.         |

| size    | 8    | Element size.            | dim   | 2    | Array dim (max 3).      |

| $S_{i}$ | 32   | Array size $(3\times)$ . | $T_i$ | 32   | Tile size $(3\times)$ . |

| wl      | 10   | Start wordline.          | trans | 2    | Transpose state.        |

(TTU) to convert between transposed and normal format, similar to prior works [15, 17].

**Execute Commands:** After the data is prepared,  $TC_{core}$  sends out commands in a small command cache (2kB) to  $TC_{L3}$  at mapped L3 banks. Commands are generated by the runtime (see §4.2) or reused if the same region is executed multiple times.  $TC_{L3}$  is a microcontroller to convert the command's bitline and tile pattern to masks for its local tiles and broadcast commands to SRAM arrays. For inter-tile shifts, it generates the control signals to configure the H tree to shift or broadcast the data, and packs the bits into NoC packets if the destination tile is mapped to another L3 bank. For compute commands, it first broadcasts constant operands (if any) to bitlines, and configures the SRAM arrays to perform the bit-serial computation (using algorithms from prior work [17]). Since commands are long latency ( $n^2 + 5n$  for n-bit integer multiply),  $TC_{L3}$  can preprocess the next command to hide the processing latency.

**Synchronization:** For sync commands,  $TC_{L3}$  reports to the other  $TC_{L3}$  the # of packets sent there since the last sync, and the total sent packets to  $TC_{core}$ . Therefore, the receiving  $TC_{L3}$  knows how many packets to expect and can report back to  $TC_{core}$  when all packets arrived. After hearing back from all  $TC_{L3}$ s,  $TC_{core}$  checks that # of sent/received packets matches before broadcasting a message to clear the barrier.

**Delayed Release of Transposed Data:** To release the transposed data,  $TC_{core}$  offloads a special store stream to evict data to the memory, which releases the reserved cache ways. To capture the reuse across program regions, e.g. iterative algorithms,  $TC_{core}$  delays releasing the data until any of the following conditions:

- Following an in-memory phase, the number of normal requests to the transposed data exceeds a threshold (we use 100k), suggesting that it is now used for in-core/near-mem computing.

- The L3 miss rate exceeds a threshold, suggesting releasing the reserved ways to reduce the pressure on the L3.

- A timer expires (we use 100k cycles).

# 5.3 Fused In-/Near-Memory Computing

One key advantage of infinity stream is to enable normal core/stream accesses to the transposed data, which allows cores/streams to be *unaware* of the data layout, providing flexibility across paradigms.

**Coherence:** Tiling constraints in §4.1 guarantees that transposed cache lines are still mapped to a single (but maybe different) L3 bank. Therefore, the coherence state can be tracked in the newly mapped L3 bank, enabling accesses to transposed data structures using normal requests when in-memory computing is not used. Before inmemory computing starts,  $TC_{core}$  evicts any dirty copies in private caches to ensure the data in L3 is up-to-date. During in-memory computing, cores are disabled from accessing the data structure by blocking the requests from private caches (setting trans in LOT to 1). However, streams at  $SE_{L3}$  can still read and write transposed

**Table 2: System and μarch Parameters (cy.: cycle)**

|                                              | *                                                                                                 |                    |                                                                                                                                           |  |

|----------------------------------------------|---------------------------------------------------------------------------------------------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------|--|

| System                                       | 2.0GHz, 8x8 Cores                                                                                 | NoC                | 32B 1 cy. link, 8x8 Mesh                                                                                                                  |  |

| OOO8 CPU<br>(8-issue)                        | 64 IQ, 72 LQ, 56 SQ+SB<br>348 Int/FP RF, 224 ROB                                                  |                    | 5-stage router, multicast<br>X-Y routing, 16 mem. ctrls                                                                                   |  |

| Func. Units                                  | 8 Int ALU/SIMD (1 cy.)<br>4 Int Mult/Div (3/12 cy.)<br>4 FP ALU/SIMD (4 cy.)<br>4 FP Div (12 cy.) | Shared<br>L3 \$    | 20 cycles, MESI<br>Static NUCA, 1kB interleave<br>256x256 SRAM array (8kB)<br>5-level H tree, 64B total BW.<br>16 arrays per way, 18 ways |  |

| L1 D/I TLB<br>L2/SE <sub>L3</sub> TLB        | 64-entry, 8-way<br>2k/1k-entry, 16-way, 8 cy.                                                     |                    | 64 banks, total 144MB                                                                                                                     |  |

|                                              |                                                                                                   | DRAM               | 3200MHz DDR4 25.6 GB/s                                                                                                                    |  |

| L1 I/D \$<br>Priv. L2 \$                     | 32KB, 8-way, 2 cy.<br>256KB, 16-way, 16 cy.                                                       | SE <sub>core</sub> | 2kB FIFO, 12 streams                                                                                                                      |  |

| Replacement<br>L1 Bingo Pf.<br>L2 Stride Pf. | Bimodal RRIP, $p = 0.03$<br>8kB PHT, 2kB region<br>16 streams, 16 pf./stream                      | SE <sub>L3</sub>   | 768 streams, 64kB buf.<br>4 cy. compute init. lat.                                                                                        |  |

|                                              |                                                                                                   | LOT                | 16 regions                                                                                                                                |  |

|                                              |                                                                                                   |                    |                                                                                                                                           |  |

Table 3: Workloads (BC: Broadcast)

| Benchmark      | Move  | Cmp.   | Parameters         |

|----------------|-------|--------|--------------------|

| stencil1d      | Shift | Elem   | 4M-entry, 10-iter  |

| stencil2d      | Shift | Elem   | 2k×2k, 10-iter     |

| stencil3d      | Shift | Elem   | 512×512×16\        |

|                |       |        | 10-iter            |

| dwt2d          | Shift | Elem   | $2k\times 2k$      |

| gauss_elim     | BC    | Elem   | $2k\times 2k$      |

| conv2d         | Shift | Elem   | 2k×2k              |

| conv3d         | BC    | Elem   | H/W=256,K=\        |

|                |       |        | 3×3, I/O=64        |

| mm/in          | BC    | Reduce | M/N/K=2k           |

| mm/out         | BC    | Elem   | Same               |

| kmeans/in      | BC    | Reduce | 32k-point,dim=128\ |

| kmeans/out     | BC    | Elem   | 128-center         |

| gather_mlp/in  | BC    | Reduce | M=32k,\            |

| gather_mlp/out | BC    | Elem   | N/K=128            |

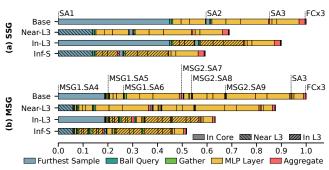

Table 4: PointNet++

| Krnl. | K, N, r, [dims]                                        |

|-------|--------------------------------------------------------|

| SA1   | 512, 32, 0.2, [64, 64, 128]                            |

| SA2   | 128, 64, 0.4, [128, 128, 256]                          |

| SA3   | 1, 128, Inf, [256, 512, 1024]                          |

| SA4   | 512, 16, 0.1, [32, 32, 64]                             |

| SA5   | 512, 32, 0.2, [64, 64, 128]                            |

| SA6   | 512, 128, 0.4, [64, 96, 128]                           |

| SA7   | 128, 16, 0.2, [64, 64, 128]                            |

| SA8   | 128, 32, 0.4, [128, 128, 256]                          |

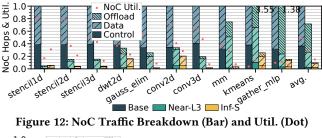

| SA9   | 128, 128, 0.8, [128, 128, 256]                         |